#include "Target/AMDGPU/AMDGPULegalizerInfo.h"

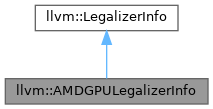

Detailed Description

Definition at line 30 of file AMDGPULegalizerInfo.h.

Constructor & Destructor Documentation

◆ AMDGPULegalizerInfo()

| AMDGPULegalizerInfo::AMDGPULegalizerInfo | ( | const GCNSubtarget & | ST, |

| const GCNTargetMachine & | TM | ||

| ) |

Definition at line 650 of file AMDGPULegalizerInfo.cpp.

References llvm::LegalityPredicates::all(), AllS32Vectors, AllS64Vectors, llvm::LegalizeRuleSet::alwaysLegal(), assert(), llvm::AMDGPUAS::BUFFER_FAT_POINTER, llvm::AMDGPUAS::BUFFER_RESOURCE, llvm::AMDGPUAS::BUFFER_STRIDED_POINTER, llvm::LegalizeMutations::changeTo(), llvm::LegalizeRuleSet::clampMaxNumElements(), llvm::LegalizeRuleSet::clampMaxNumElementsStrict(), llvm::LegalizeRuleSet::clampScalar(), llvm::LegalizeRuleSet::clampScalarOrElt(), llvm::AMDGPUAS::CONSTANT_ADDRESS, llvm::AMDGPUAS::CONSTANT_ADDRESS_32BIT, llvm::LegalizeRuleSet::custom(), llvm::LegalizeRuleSet::customFor(), llvm::LegalizeRuleSet::customIf(), elementTypeIsLegal(), llvm::LegalizeRuleSet::fewerElementsIf(), fewerEltsToSize64Vector(), llvm::AMDGPUAS::FLAT_ADDRESS, llvm::LegalizerInfo::getActionDefinitionsBuilder(), llvm::AMDGPUAS::GLOBAL_ADDRESS, llvm::AMDGPUSubtarget::has16BitInsts(), llvm::GCNSubtarget::hasAddNoCarry(), llvm::GCNSubtarget::hasFractBug(), llvm::GCNSubtarget::hasIntClamp(), llvm::GCNSubtarget::hasMad64_32(), llvm::GCNSubtarget::hasMadF16(), llvm::AMDGPUSubtarget::hasMadMacF32Insts(), llvm::GCNSubtarget::hasPackedFP32Ops(), llvm::GCNSubtarget::hasScalarAddSub64(), llvm::GCNSubtarget::hasScalarSMulU64(), llvm::AMDGPUSubtarget::hasVOP3PInsts(), llvm::LegalityPredicates::isPointer(), isRegisterClassType(), isRegisterType(), llvm::LegalityPredicates::isScalar(), isSmallOddVector(), llvm::LegalizeRuleSet::legalFor(), llvm::LegalizeRuleSet::legalIf(), llvm::AMDGPUAS::LOCAL_ADDRESS, llvm::LegalizeRuleSet::lower(), llvm::LegalizeRuleSet::maxScalar(), MaxScalar, llvm::LegalizeRuleSet::minScalar(), llvm::LegalizeRuleSet::moreElementsIf(), llvm::Mul, oneMoreElement(), llvm::LLT::pointer(), llvm::AMDGPUAS::PRIVATE_ADDRESS, llvm::AMDGPUAS::REGION_ADDRESS, S1, S128, S16, S256, S32, S64, S8, llvm::LegalizeMutations::scalarize(), llvm::LegalizeRuleSet::scalarize(), TM, llvm::LegalityPredicates::typeIs(), llvm::LegalityPredicates::typeIsNot(), V2S16, V2S32, V2S8, V4S16, vectorWiderThan(), llvm::LegalizeRuleSet::widenScalarToNextMultipleOf(), and llvm::LegalizeRuleSet::widenScalarToNextPow2().

Member Function Documentation

◆ buildAbsGlobalAddress()

| void AMDGPULegalizerInfo::buildAbsGlobalAddress | ( | Register | DstReg, |

| LLT | PtrTy, | ||

| MachineIRBuilder & | B, | ||

| const GlobalValue * | GV, | ||

| MachineRegisterInfo & | MRI | ||

| ) | const |

Definition at line 2854 of file AMDGPULegalizerInfo.cpp.

References assert(), B, llvm::LLT::getSizeInBits(), llvm::SIInstrInfo::MO_ABS32_HI, llvm::SIInstrInfo::MO_ABS32_LO, MRI, S32, and llvm::LLT::scalar().

Referenced by legalizeGlobalValue().

◆ buildMultiply()

| void AMDGPULegalizerInfo::buildMultiply | ( | LegalizerHelper & | Helper, |

| MutableArrayRef< Register > | Accum, | ||

| ArrayRef< Register > | Src0, | ||

| ArrayRef< Register > | Src1, | ||

| bool | UsePartialMad64_32, | ||

| bool | SeparateOddAlignedProducts | ||

| ) | const |

Definition at line 3826 of file AMDGPULegalizerInfo.cpp.

References llvm::Add, assert(), B, llvm::MutableArrayRef< T >::drop_front(), llvm::LegalizerHelper::getKnownBits(), llvm::GISelKnownBits::getKnownBits(), llvm::Hi, llvm::KnownBits::isZero(), llvm::Lo, llvm::LegalizerHelper::MIRBuilder, llvm::Mul, llvm::SmallVectorTemplateBase< T, bool >::push_back(), S1, S32, S64, llvm::LLT::scalar(), llvm::ArrayRef< T >::size(), and llvm::MutableArrayRef< T >::take_front().

Referenced by legalizeMul().

◆ buildPCRelGlobalAddress()

| bool AMDGPULegalizerInfo::buildPCRelGlobalAddress | ( | Register | DstReg, |

| LLT | PtrTy, | ||

| MachineIRBuilder & | B, | ||

| const GlobalValue * | GV, | ||

| int64_t | Offset, | ||

| unsigned | GAFlags = SIInstrInfo::MO_NONE |

||

| ) | const |

Definition at line 2801 of file AMDGPULegalizerInfo.cpp.

References llvm::MachineInstrBuilder::addGlobalAddress(), llvm::MachineInstrBuilder::addImm(), assert(), B, llvm::AMDGPUAS::CONSTANT_ADDRESS, llvm::LLT::getSizeInBits(), llvm::SIInstrInfo::MO_NONE, llvm::Offset, and llvm::LLT::pointer().

Referenced by legalizeGlobalValue().

◆ fixStoreSourceType()

| Register AMDGPULegalizerInfo::fixStoreSourceType | ( | MachineIRBuilder & | B, |

| Register | VData, | ||

| bool | IsFormat | ||

| ) | const |

Definition at line 5628 of file AMDGPULegalizerInfo.cpp.

References B, castBufferRsrcToV4I32(), llvm::LLT::getElementType(), llvm::LLT::getNumElements(), handleD16VData(), hasBufferRsrcWorkaround(), llvm::LLT::isVector(), MRI, S16, and llvm::LLT::scalar().

Referenced by legalizeBufferStore().

◆ getImplicitArgPtr()

| bool AMDGPULegalizerInfo::getImplicitArgPtr | ( | Register | DstReg, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 5390 of file AMDGPULegalizerInfo.cpp.

References B, llvm::AMDGPUTargetLowering::FIRST_IMPLICIT, llvm::AMDGPUTargetLowering::getImplicitParameterOffset(), llvm::LLT::getSizeInBits(), llvm::GCNSubtarget::getTargetLowering(), llvm::AMDGPUFunctionArgInfo::KERNARG_SEGMENT_PTR, loadInputValue(), MRI, llvm::Offset, and llvm::LLT::scalar().

Referenced by legalizeImplicitArgPtr().

◆ getKernargParameterPtr()

| Register AMDGPULegalizerInfo::getKernargParameterPtr | ( | MachineIRBuilder & | B, |

| int64_t | Offset | ||

| ) | const |

Definition at line 4353 of file AMDGPULegalizerInfo.cpp.

References B, llvm::AMDGPUAS::CONSTANT_ADDRESS, llvm::AMDGPUFunctionArgInfo::KERNARG_SEGMENT_PTR, llvm_unreachable, loadInputValue(), llvm::Offset, llvm::LLT::pointer(), and llvm::LLT::scalar().

Referenced by legalizeKernargMemParameter().

◆ getLDSKernelId()

| bool AMDGPULegalizerInfo::getLDSKernelId | ( | Register | DstReg, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 5470 of file AMDGPULegalizerInfo.cpp.

References B, F, and llvm::AMDGPUMachineFunction::getLDSKernelIdMetadata().

Referenced by legalizeLDSKernelId().

◆ getScaledLogInput()

| std::pair< Register, Register > AMDGPULegalizerInfo::getScaledLogInput | ( | MachineIRBuilder & | B, |

| Register | Src, | ||

| unsigned | Flags | ||

| ) | const |

Definition at line 3224 of file AMDGPULegalizerInfo.cpp.

References B, llvm::CmpInst::FCMP_OLT, llvm::APFloat::getSmallestNormalized(), llvm::APFloatBase::IEEEsingle(), needsDenormHandlingF32(), and llvm::LLT::scalar().

Referenced by legalizeFlog2(), legalizeFlogCommon(), and legalizeFlogUnsafe().

◆ getSegmentAperture()

| Register AMDGPULegalizerInfo::getSegmentAperture | ( | unsigned | AddrSpace, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 2150 of file AMDGPULegalizerInfo.cpp.

References llvm::AMDGPU::AMDHSA_COV5, assert(), B, llvm::commonAlignment(), llvm::AMDGPUAS::CONSTANT_ADDRESS, llvm::AMDGPU::getAMDHSACodeObjectVersion(), llvm::MachineFunction::getFunction(), llvm::MachineFunction::getMachineMemOperand(), llvm::GlobalValue::getParent(), llvm::MachineFunction::getSubtarget(), llvm::AMDGPUFunctionArgInfo::KERNARG_SEGMENT_PTR, loadInputValue(), llvm::AMDGPUAS::LOCAL_ADDRESS, llvm::MachineMemOperand::MODereferenceable, llvm::MachineMemOperand::MOInvariant, llvm::MachineMemOperand::MOLoad, MRI, llvm::Offset, llvm::LLT::pointer(), llvm::AMDGPUAS::PRIVATE_ADDRESS, llvm::AMDGPUTargetLowering::PRIVATE_BASE, llvm::AMDGPUFunctionArgInfo::QUEUE_PTR, S32, S64, llvm::LLT::scalar(), and llvm::AMDGPUTargetLowering::SHARED_BASE.

Referenced by legalizeAddrSpaceCast(), and legalizeIsAddrSpace().

◆ handleD16VData()

| Register AMDGPULegalizerInfo::handleD16VData | ( | MachineIRBuilder & | B, |

| MachineRegisterInfo & | MRI, | ||

| Register | Reg, | ||

| bool | ImageStore = false |

||

| ) | const |

Handle register layout difference for f16 images for some subtargets.

Definition at line 5565 of file AMDGPULegalizerInfo.cpp.

References assert(), B, llvm::LLT::fixed_vector(), llvm::LLT::getElementType(), llvm::LLT::getNumElements(), llvm::GCNSubtarget::hasImageStoreD16Bug(), llvm::GCNSubtarget::hasUnpackedD16VMem(), I, llvm::LLT::isVector(), llvm_unreachable, MRI, llvm::SmallVectorTemplateBase< T, bool >::push_back(), llvm::SmallVectorImpl< T >::resize(), S16, S32, and llvm::LLT::scalar().

Referenced by fixStoreSourceType(), and legalizeImageIntrinsic().

◆ legalizeAddrSpaceCast()

| bool AMDGPULegalizerInfo::legalizeAddrSpaceCast | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 2257 of file AMDGPULegalizerInfo.cpp.

References assert(), B, llvm::AMDGPUAS::CONSTANT_ADDRESS_32BIT, llvm::LLVMContext::diagnose(), llvm::AMDGPUAS::FLAT_ADDRESS, llvm::LLT::getAddressSpace(), llvm::Function::getContext(), llvm::MachineFunction::getFunction(), llvm::MachineFunction::getInfo(), getSegmentAperture(), llvm::LLT::getSizeInBits(), llvm::MachineFunction::getTarget(), llvm::CmpInst::ICMP_NE, Info, isKnownNonNull(), llvm::Register::isValid(), llvm::LLT::isVector(), llvm::AMDGPUAS::LOCAL_ADDRESS, MI, MRI, llvm::AMDGPUAS::PRIVATE_ADDRESS, S32, llvm::LLT::scalar(), and TM.

Referenced by legalizeCustom(), and legalizeIntrinsic().

◆ legalizeAtomicCmpXChg()

| bool AMDGPULegalizerInfo::legalizeAtomicCmpXChg | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 3154 of file AMDGPULegalizerInfo.cpp.

References assert(), B, llvm::LLT::fixed_vector(), getReg(), llvm::AMDGPU::isFlatGlobalAddrSpace(), MI, and MRI.

Referenced by legalizeCustom().

◆ legalizeBufferAtomic()

| bool AMDGPULegalizerInfo::legalizeBufferAtomic | ( | MachineInstr & | MI, |

| MachineIRBuilder & | B, | ||

| Intrinsic::ID | IID | ||

| ) | const |

Definition at line 5997 of file AMDGPULegalizerInfo.cpp.

References B, castBufferRsrcArgToV4I32(), getBufferAtomicPseudo(), MI, llvm::LLT::scalar(), and splitBufferOffsets().

Referenced by legalizeIntrinsic().

◆ legalizeBufferLoad()

| bool AMDGPULegalizerInfo::legalizeBufferLoad | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B, | ||

| bool | IsFormat, | ||

| bool | IsTyped | ||

| ) | const |

Definition at line 5763 of file AMDGPULegalizerInfo.cpp.

References assert(), B, buildBufferLoad(), castBufferRsrcArgToV4I32(), castBufferRsrcFromV4I32(), llvm::LLT::changeElementSize(), llvm::divideCeil(), llvm::LLT::fixed_vector(), llvm::Format, llvm::MachineMemOperand::getMemoryType(), llvm::LLT::getScalarType(), llvm::LLT::getSizeInBits(), hasBufferRsrcWorkaround(), llvm::GCNSubtarget::hasUnpackedD16VMem(), I, llvm::LLT::isVector(), MI, MRI, N, llvm::SmallVectorTemplateBase< T, bool >::push_back(), S32, llvm::LLT::scalar(), splitBufferOffsets(), and llvm::SmallVectorImpl< T >::truncate().

Referenced by legalizeIntrinsic().

◆ legalizeBufferStore()

| bool AMDGPULegalizerInfo::legalizeBufferStore | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B, | ||

| bool | IsTyped, | ||

| bool | IsFormat | ||

| ) | const |

Definition at line 5655 of file AMDGPULegalizerInfo.cpp.

References B, castBufferRsrcArgToV4I32(), fixStoreSourceType(), llvm::Format, llvm::LLT::getScalarType(), llvm::MachineMemOperand::getSize(), llvm::LLT::getSizeInBits(), llvm::LocationSize::getValue(), MI, MRI, S32, llvm::LLT::scalar(), and splitBufferOffsets().

Referenced by legalizeIntrinsic().

◆ legalizeBuildVector()

| bool AMDGPULegalizerInfo::legalizeBuildVector | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 3794 of file AMDGPULegalizerInfo.cpp.

References assert(), B, llvm::LLT::fixed_vector(), Merge, MI, MRI, S16, S32, and llvm::LLT::scalar().

Referenced by legalizeCustom().

◆ legalizeBVHIntrinsic()

| bool AMDGPULegalizerInfo::legalizeBVHIntrinsic | ( | MachineInstr & | MI, |

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 6768 of file AMDGPULegalizerInfo.cpp.

References assert(), B, llvm::SmallVectorImpl< T >::clear(), llvm::LLT::fixed_vector(), llvm::AMDGPU::getMIMGOpcode(), llvm::GCNSubtarget::getNSAMaxSize(), llvm::GCNSubtarget::hasGFX10_AEncoding(), llvm::GCNSubtarget::hasNSAEncoding(), llvm::AMDGPU::isGFX11(), llvm::AMDGPU::isGFX11Plus(), llvm::AMDGPU::isGFX12Plus(), MI, MRI, llvm::SmallVectorTemplateBase< T, bool >::push_back(), R2, S16, S32, llvm::LLT::scalar(), llvm::SmallVectorBase< Size_T >::size(), V2S16, and V3S32.

Referenced by legalizeIntrinsic().

◆ legalizeCTLZ_CTTZ()

| bool AMDGPULegalizerInfo::legalizeCTLZ_CTTZ | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 4130 of file AMDGPULegalizerInfo.cpp.

References B, llvm::LLT::getSizeInBits(), MI, and MRI.

Referenced by legalizeCustom().

◆ legalizeCustom()

|

overridevirtual |

Called for instructions with the Custom LegalizationAction.

Reimplemented from llvm::LegalizerInfo.

Definition at line 2046 of file AMDGPULegalizerInfo.cpp.

References B, legalizeAddrSpaceCast(), legalizeAtomicCmpXChg(), legalizeBuildVector(), legalizeCTLZ_CTTZ(), legalizeDebugTrap(), legalizeExtractVectorElt(), legalizeFceil(), legalizeFDIV(), legalizeFExp(), legalizeFExp2(), legalizeFFloor(), legalizeFFREXP(), legalizeFlog2(), legalizeFlogCommon(), legalizeFMad(), legalizeFPow(), legalizeFPTOI(), legalizeFPTruncRound(), legalizeFrem(), legalizeFroundeven(), legalizeFSQRT(), legalizeGetFPEnv(), legalizeGlobalValue(), legalizeInsertVectorElt(), legalizeIntrinsicTrunc(), legalizeITOFP(), legalizeLoad(), legalizeMinNumMaxNum(), legalizeMul(), legalizeSetFPEnv(), legalizeSignedDIV_REM(), legalizeSinCos(), legalizeStackSave(), legalizeStore(), legalizeTrap(), legalizeUnsignedDIV_REM(), llvm_unreachable, MI, llvm::LegalizerHelper::MIRBuilder, and MRI.

◆ legalizeDebugTrap()

| bool AMDGPULegalizerInfo::legalizeDebugTrap | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 6746 of file AMDGPULegalizerInfo.cpp.

References llvm::GCNSubtarget::AMDHSA, B, llvm::LLVMContext::diagnose(), llvm::DS_Warning, llvm::GCNSubtarget::getTrapHandlerAbi(), llvm::GCNSubtarget::isTrapHandlerEnabled(), llvm::GCNSubtarget::LLVMAMDHSADebugTrap, and MI.

Referenced by legalizeCustom().

◆ legalizeDSAtomicFPIntrinsic()

| bool AMDGPULegalizerInfo::legalizeDSAtomicFPIntrinsic | ( | LegalizerHelper & | Helper, |

| MachineInstr & | MI, | ||

| Intrinsic::ID | IID | ||

| ) | const |

Definition at line 5372 of file AMDGPULegalizerInfo.cpp.

References llvm::GISelChangeObserver::changedInstr(), llvm::GISelChangeObserver::changingInstr(), getDSFPAtomicOpcode(), llvm::GCNSubtarget::getInstrInfo(), I, MI, and llvm::LegalizerHelper::Observer.

Referenced by legalizeIntrinsic().

◆ legalizeExtractVectorElt()

| bool AMDGPULegalizerInfo::legalizeExtractVectorElt | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 2660 of file AMDGPULegalizerInfo.cpp.

References assert(), B, llvm::LLT::changeElementType(), llvm::LLT::getElementType(), llvm::getIConstantVRegValWithLookThrough(), llvm::LLT::getNumElements(), llvm::LLT::getSizeInBits(), llvm::LLT::isPointer(), MI, MRI, and llvm::LLT::scalar().

Referenced by legalizeCustom().

◆ legalizeFastUnsafeFDIV()

| bool AMDGPULegalizerInfo::legalizeFastUnsafeFDIV | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 4716 of file AMDGPULegalizerInfo.cpp.

References B, llvm::MachineInstr::FmAfn, llvm::MachineInstr::FmArcp, llvm::getConstantFPVRegVal(), llvm::MachineFunction::getTarget(), LHS, MI, MRI, llvm::TargetMachine::Options, RHS, llvm::LLT::scalar(), and llvm::TargetOptions::UnsafeFPMath.

Referenced by legalizeFDIV16(), and legalizeFDIV32().

◆ legalizeFastUnsafeFDIV64()

| bool AMDGPULegalizerInfo::legalizeFastUnsafeFDIV64 | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 4778 of file AMDGPULegalizerInfo.cpp.

References B, llvm::MachineInstr::FmAfn, llvm::MachineFunction::getTarget(), MI, MRI, llvm::TargetMachine::Options, llvm::TargetOptions::UnsafeFPMath, X, and Y.

Referenced by legalizeFDIV64().

◆ legalizeFceil()

| bool AMDGPULegalizerInfo::legalizeFceil | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 2406 of file AMDGPULegalizerInfo.cpp.

References llvm::Add, assert(), B, llvm::CmpInst::FCMP_OGT, llvm::CmpInst::FCMP_ONE, MI, MRI, S1, S64, and llvm::LLT::scalar().

Referenced by legalizeCustom().

◆ legalizeFDIV()

| bool AMDGPULegalizerInfo::legalizeFDIV | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 4389 of file AMDGPULegalizerInfo.cpp.

References B, legalizeFDIV16(), legalizeFDIV32(), legalizeFDIV64(), MI, MRI, S16, S32, S64, and llvm::LLT::scalar().

Referenced by legalizeCustom().

◆ legalizeFDIV16()

| bool AMDGPULegalizerInfo::legalizeFDIV16 | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 4815 of file AMDGPULegalizerInfo.cpp.

References B, legalizeFastUnsafeFDIV(), LHS, MI, MRI, RHS, S16, S32, and llvm::LLT::scalar().

Referenced by legalizeFDIV().

◆ legalizeFDIV32()

| bool AMDGPULegalizerInfo::legalizeFDIV32 | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 4877 of file AMDGPULegalizerInfo.cpp.

References assert(), B, llvm::DenormalMode::Dynamic, llvm::DenormalMode::getIEEE(), llvm::SIMachineFunctionInfo::getMode(), legalizeFastUnsafeFDIV(), LHS, MI, MRI, llvm::Mul, RHS, S1, S32, llvm::LLT::scalar(), SPDenormModeBitField, and toggleSPDenormMode().

Referenced by legalizeFDIV().

◆ legalizeFDIV64()

| bool AMDGPULegalizerInfo::legalizeFDIV64 | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 4964 of file AMDGPULegalizerInfo.cpp.

References B, llvm::GCNSubtarget::hasUsableDivScaleConditionOutput(), llvm::CmpInst::ICMP_EQ, legalizeFastUnsafeFDIV64(), LHS, MI, MRI, llvm::Mul, RHS, S1, S32, S64, and llvm::LLT::scalar().

Referenced by legalizeFDIV().

◆ legalizeFDIVFastIntrin()

| bool AMDGPULegalizerInfo::legalizeFDIVFastIntrin | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 5080 of file AMDGPULegalizerInfo.cpp.

References B, llvm::CmpInst::FCMP_OGT, LHS, MI, RHS, S1, S32, and llvm::LLT::scalar().

Referenced by legalizeIntrinsic().

◆ legalizeFExp()

| bool AMDGPULegalizerInfo::legalizeFExp | ( | MachineInstr & | MI, |

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 3547 of file AMDGPULegalizerInfo.cpp.

References A, allowApproxFunc(), assert(), B, llvm::CallingConv::C, CC, CH, llvm::CmpInst::FCMP_OGT, llvm::CmpInst::FCMP_OLT, llvm::MachineInstr::FmNoInfs, llvm::APFloat::getInf(), getMad(), llvm::MachineFunction::getTarget(), llvm::AMDGPUSubtarget::hasFastFMAF32(), llvm::APFloatBase::IEEEsingle(), legalizeFExpUnsafe(), llvm::numbers::log2ef, MI, MRI, llvm::TargetMachine::Options, Options, llvm::LLT::scalar(), and X.

Referenced by legalizeCustom().

◆ legalizeFExp2()

| bool AMDGPULegalizerInfo::legalizeFExp2 | ( | MachineInstr & | MI, |

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 3449 of file AMDGPULegalizerInfo.cpp.

References assert(), B, llvm::CmpInst::FCMP_OLT, llvm::Log2(), MI, needsDenormHandlingF32(), and llvm::LLT::scalar().

Referenced by legalizeCustom().

◆ legalizeFExpUnsafe()

| bool AMDGPULegalizerInfo::legalizeFExpUnsafe | ( | MachineIRBuilder & | B, |

| Register | Dst, | ||

| Register | Src, | ||

| unsigned | Flags | ||

| ) | const |

Definition at line 3507 of file AMDGPULegalizerInfo.cpp.

References B, llvm::CmpInst::FCMP_OLT, llvm::numbers::log2e, llvm::Mul, needsDenormHandlingF32(), llvm::LLT::scalar(), and X.

Referenced by legalizeFExp().

◆ legalizeFFloor()

| bool AMDGPULegalizerInfo::legalizeFFloor | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 3735 of file AMDGPULegalizerInfo.cpp.

References assert(), B, llvm::CmpInst::FCMP_ORD, llvm::LLT::float64(), llvm::MachineInstr::FmNoNans, llvm::SIMachineFunctionInfo::getMode(), llvm::GCNSubtarget::hasFractBug(), llvm::SIModeRegisterDefaults::IEEE, MI, MRI, S1, llvm::LLT::scalar(), and stripAnySourceMods().

Referenced by legalizeCustom().

◆ legalizeFFREXP()

| bool AMDGPULegalizerInfo::legalizeFFREXP | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 5045 of file AMDGPULegalizerInfo.cpp.

References B, llvm::CmpInst::FCMP_OLT, llvm::getFltSemanticForLLT(), llvm::APFloat::getInf(), llvm::GCNSubtarget::hasFractBug(), MI, MRI, and llvm::LLT::scalar().

Referenced by legalizeCustom().

◆ legalizeFlog2()

| bool AMDGPULegalizerInfo::legalizeFlog2 | ( | MachineInstr & | MI, |

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 3244 of file AMDGPULegalizerInfo.cpp.

References assert(), B, getScaledLogInput(), llvm::Log2(), MI, and llvm::LLT::scalar().

Referenced by legalizeCustom().

◆ legalizeFlogCommon()

| bool AMDGPULegalizerInfo::legalizeFlogCommon | ( | MachineInstr & | MI, |

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 3300 of file AMDGPULegalizerInfo.cpp.

References assert(), B, llvm::CallingConv::C, CC, CH, llvm::CmpInst::FCMP_OLT, llvm::MachineInstr::FmAfn, llvm::MachineInstr::FmNoInfs, llvm::MachineInstr::FmNoNans, llvm::APFloat::getInf(), getMad(), getScaledLogInput(), llvm::MachineFunction::getTarget(), llvm::AMDGPUSubtarget::has16BitInsts(), llvm::AMDGPUSubtarget::hasFastFMAF32(), llvm::APFloatBase::IEEEsingle(), legalizeFlogUnsafe(), MI, MRI, llvm::LLT::scalar(), TM, X, and Y.

Referenced by legalizeCustom().

◆ legalizeFlogUnsafe()

| bool AMDGPULegalizerInfo::legalizeFlogUnsafe | ( | MachineIRBuilder & | B, |

| Register | Dst, | ||

| Register | Src, | ||

| bool | IsLog10, | ||

| unsigned | Flags | ||

| ) | const |

Definition at line 3408 of file AMDGPULegalizerInfo.cpp.

References B, getScaledLogInput(), llvm::AMDGPUSubtarget::hasFastFMAF32(), llvm::numbers::ln10, llvm::numbers::ln2, llvm::Mul, and llvm::LLT::scalar().

Referenced by legalizeFlogCommon().

◆ legalizeFMad()

| bool AMDGPULegalizerInfo::legalizeFMad | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 3130 of file AMDGPULegalizerInfo.cpp.

References assert(), B, llvm::LLT::float16(), llvm::LLT::float32(), llvm::SIModeRegisterDefaults::FP32Denormals, llvm::SIModeRegisterDefaults::FP64FP16Denormals, llvm::MachineFunction::getInfo(), llvm::SIMachineFunctionInfo::getMode(), llvm::DenormalMode::getPreserveSign(), llvm::LLT::isScalar(), llvm::LegalizerHelper::Legalized, llvm::LegalizerHelper::lowerFMad(), MI, and MRI.

Referenced by legalizeCustom().

◆ legalizeFPow()

| bool AMDGPULegalizerInfo::legalizeFPow | ( | MachineInstr & | MI, |

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 3689 of file AMDGPULegalizerInfo.cpp.

References B, llvm::LLT::float16(), llvm::LLT::float32(), MI, and llvm::Mul.

Referenced by legalizeCustom().

◆ legalizeFPTOI()

| bool AMDGPULegalizerInfo::legalizeFPTOI | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B, | ||

| bool | Signed | ||

| ) | const |

Definition at line 2571 of file AMDGPULegalizerInfo.cpp.

References assert(), B, llvm::Hi, llvm::Lo, MI, MRI, llvm::Mul, S32, S64, llvm::LLT::scalar(), and Signed.

Referenced by legalizeCustom().

◆ legalizeFPTruncRound()

| bool AMDGPULegalizerInfo::legalizeFPTruncRound | ( | MachineInstr & | MI, |

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 6921 of file AMDGPULegalizerInfo.cpp.

References B, MI, llvm::TowardNegative, and llvm::TowardPositive.

Referenced by legalizeCustom().

◆ legalizeFrem()

| bool AMDGPULegalizerInfo::legalizeFrem | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 2435 of file AMDGPULegalizerInfo.cpp.

Referenced by legalizeCustom().

◆ legalizeFroundeven()

| bool AMDGPULegalizerInfo::legalizeFroundeven | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 2380 of file AMDGPULegalizerInfo.cpp.

References assert(), B, Cond, llvm::CmpInst::FCMP_OGT, llvm::LLT::getSizeInBits(), llvm::APFloatBase::IEEEdouble(), llvm::LLT::isScalar(), MI, MRI, and llvm::LLT::scalar().

Referenced by legalizeCustom().

◆ legalizeFSQRT()

| bool AMDGPULegalizerInfo::legalizeFSQRT | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 5297 of file AMDGPULegalizerInfo.cpp.

References B, legalizeFSQRTF16(), legalizeFSQRTF32(), legalizeFSQRTF64(), MI, MRI, and llvm::LLT::scalar().

Referenced by legalizeCustom().

◆ legalizeFSQRTF16()

| bool AMDGPULegalizerInfo::legalizeFSQRTF16 | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 5115 of file AMDGPULegalizerInfo.cpp.

References assert(), B, llvm::AMDGPUSubtarget::has16BitInsts(), llvm::Log2(), MI, and llvm::LLT::scalar().

Referenced by legalizeFSQRT().

◆ legalizeFSQRTF32()

| bool AMDGPULegalizerInfo::legalizeFSQRTF32 | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 5132 of file AMDGPULegalizerInfo.cpp.

References allowApproxFunc(), B, llvm::CmpInst::FCMP_OGT, llvm::CmpInst::FCMP_OLE, llvm::fcPosInf, llvm::fcZero, MI, MRI, needsDenormHandlingF32(), S1, llvm::LLT::scalar(), and X.

Referenced by legalizeFSQRT().

◆ legalizeFSQRTF64()

| bool AMDGPULegalizerInfo::legalizeFSQRTF64 | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 5213 of file AMDGPULegalizerInfo.cpp.

References assert(), B, llvm::CmpInst::FCMP_OLT, llvm::fcPosInf, llvm::fcZero, MI, MRI, S1, S32, llvm::LLT::scalar(), and X.

Referenced by legalizeFSQRT().

◆ legalizeGetFPEnv()

| bool AMDGPULegalizerInfo::legalizeGetFPEnv | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 6973 of file AMDGPULegalizerInfo.cpp.

References B, FPEnvModeBitField, FPEnvTrapBitField, MI, MRI, S32, and S64.

Referenced by legalizeCustom().

◆ legalizeGlobalValue()

| bool AMDGPULegalizerInfo::legalizeGlobalValue | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 2909 of file AMDGPULegalizerInfo.cpp.

References llvm::AMDGPUMachineFunction::allocateLDSGlobal(), B, buildAbsGlobalAddress(), buildPCRelGlobalAddress(), llvm::AMDGPUAS::CONSTANT_ADDRESS, llvm::LLVMContext::diagnose(), llvm::DS_Warning, llvm::StringRef::equals(), llvm::LLT::getAddressSpace(), llvm::Function::getContext(), llvm::MachineFunction::getFunction(), llvm::MachinePointerInfo::getGOT(), llvm::MachineFunction::getInfo(), llvm::MachineFunction::getMachineMemOperand(), llvm::Value::getName(), llvm::LLT::getSizeInBits(), llvm::GCNSubtarget::getTargetLowering(), llvm::GlobalValue::getValueType(), llvm::GlobalValue::hasExternalLinkage(), llvm::AMDGPUSubtarget::isAmdPalOS(), llvm::AMDGPUSubtarget::isMesa3DOS(), llvm::AMDGPUMachineFunction::isModuleEntryFunction(), llvm::AMDGPUAS::LOCAL_ADDRESS, MI, llvm::SIInstrInfo::MO_ABS32_LO, llvm::SIInstrInfo::MO_GOTPCREL32, llvm::SIInstrInfo::MO_REL32, llvm::MachineMemOperand::MODereferenceable, llvm::MachineMemOperand::MOInvariant, llvm::MachineMemOperand::MOLoad, MRI, llvm::LLT::pointer(), llvm::AMDGPUAS::REGION_ADDRESS, S32, llvm::LLT::scalar(), llvm::AMDGPUMachineFunction::setDynLDSAlign(), llvm::SITargetLowering::shouldEmitFixup(), llvm::SITargetLowering::shouldEmitPCReloc(), and llvm::SITargetLowering::shouldUseLDSConstAddress().

Referenced by legalizeCustom().

◆ legalizeImageIntrinsic()

| bool AMDGPULegalizerInfo::legalizeImageIntrinsic | ( | MachineInstr & | MI, |

| MachineIRBuilder & | B, | ||

| GISelChangeObserver & | Observer, | ||

| const AMDGPU::ImageDimIntrinsicInfo * | Intr | ||

| ) | const |

Rewrite image intrinsics to use register layouts expected by the subtarget.

Depending on the subtarget, load/store with 16-bit element data need to be rewritten to use the low half of 32-bit registers, or directly use a packed layout. 16-bit addresses should also sometimes be packed into 32-bit registers.

We don't want to directly select image instructions just yet, but also want to exposes all register repacking to the legalizer/combiners. We also don't want a selected instruction entering RegBankSelect. In order to avoid defining a multitude of intermediate image instructions, directly hack on the intrinsic's arguments. In cases like a16 addresses, this requires padding now unnecessary arguments with $noreg.

Definition at line 6165 of file AMDGPULegalizerInfo.cpp.

References assert(), llvm::AMDGPU::MIMGBaseOpcodeInfo::Atomic, llvm::AMDGPU::MIMGBaseOpcodeInfo::AtomicX2, B, llvm::AMDGPU::MIMGBaseOpcodeInfo::BaseOpcode, llvm::GISelChangeObserver::changedInstr(), llvm::LLT::changeElementCount(), llvm::GISelChangeObserver::changingInstr(), Concat, convertImageAddrToPacked(), llvm::MachineOperand::CreateImm(), llvm::LLT::fixed_vector(), llvm::AMDGPU::MIMGBaseOpcodeInfo::Gather4, llvm::ElementCount::getFixed(), llvm::SrcOp::getImm(), llvm::AMDGPU::getMIMGBaseOpcodeInfo(), llvm::GCNSubtarget::getNSAMaxSize(), llvm::GCNSubtarget::getNSAThreshold(), llvm::LLT::getNumElements(), llvm::SrcOp::getReg(), llvm::LLT::getScalarType(), llvm::LLT::getSizeInBits(), llvm::AMDGPU::MIMGBaseOpcodeInfo::Gradients, handleD16VData(), llvm::GCNSubtarget::hasA16(), llvm::GCNSubtarget::hasG16(), llvm::GCNSubtarget::hasNSAEncoding(), llvm::GCNSubtarget::hasPartialNSAEncoding(), llvm::GCNSubtarget::hasUnpackedD16VMem(), I, Intr, llvm::LLT::isVector(), llvm::make_scope_exit(), MI, MRI, packImage16bitOpsToDwords(), llvm::popcount(), llvm::SmallVectorTemplateBase< T, bool >::push_back(), llvm::SmallVectorImpl< T >::resize(), S16, S32, llvm::AMDGPU::MIMGBaseOpcodeInfo::Sampler, llvm::LLT::scalar(), llvm::LLT::scalarOrVector(), llvm::SmallVectorBase< Size_T >::size(), llvm::AMDGPU::MIMGBaseOpcodeInfo::Store, V2S16, and V4S16.

Referenced by legalizeIntrinsic().

◆ legalizeImplicitArgPtr()

| bool AMDGPULegalizerInfo::legalizeImplicitArgPtr | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 5453 of file AMDGPULegalizerInfo.cpp.

References B, getImplicitArgPtr(), llvm::AMDGPUFunctionArgInfo::IMPLICIT_ARG_PTR, llvm::AMDGPUMachineFunction::isEntryFunction(), legalizePreloadedArgIntrin(), MI, and MRI.

Referenced by legalizeIntrinsic().

◆ legalizeInsertVectorElt()

| bool AMDGPULegalizerInfo::legalizeInsertVectorElt | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 2711 of file AMDGPULegalizerInfo.cpp.

References assert(), B, llvm::LLT::changeElementType(), llvm::LLT::getElementType(), llvm::getIConstantVRegValWithLookThrough(), llvm::LLT::getNumElements(), llvm::LLT::getSizeInBits(), llvm::LLT::isPointer(), MI, MRI, llvm::SmallVectorTemplateBase< T, bool >::push_back(), and llvm::LLT::scalar().

Referenced by legalizeCustom().

◆ legalizeIntrinsic()

|

overridevirtual |

- Returns

- true if MI is either legal or has been legalized and false if not legal. Return true if MI is either legal or has been legalized and false if not legal.

Reimplemented from llvm::LegalizerInfo.

Definition at line 7013 of file AMDGPULegalizerInfo.cpp.

References B, llvm::GISelChangeObserver::changedInstr(), llvm::GISelChangeObserver::changingInstr(), llvm::AMDGPUFunctionArgInfo::DISPATCH_ID, llvm::AMDGPUFunctionArgInfo::DISPATCH_PTR, llvm::AMDGPU::getImageDimIntrinsicInfo(), llvm::MachineInstr::getOperand(), llvm::AMDGPUSubtarget::getWavefrontSize(), llvm::SI::KernelInputOffsets::GLOBAL_SIZE_X, llvm::SI::KernelInputOffsets::GLOBAL_SIZE_Y, llvm::SI::KernelInputOffsets::GLOBAL_SIZE_Z, llvm::AMDGPUFunctionArgInfo::IMPLICIT_BUFFER_PTR, llvm::AMDGPU::isKernel(), llvm::AMDGPUFunctionArgInfo::KERNARG_SEGMENT_PTR, llvm::AMDGPUFunctionArgInfo::LDS_KERNEL_ID, legalizeAddrSpaceCast(), legalizeBufferAtomic(), legalizeBufferLoad(), legalizeBufferStore(), legalizeBVHIntrinsic(), legalizeDSAtomicFPIntrinsic(), legalizeFDIVFastIntrin(), legalizeImageIntrinsic(), legalizeImplicitArgPtr(), legalizeIsAddrSpace(), legalizeKernargMemParameter(), legalizePointerAsRsrcIntrin(), legalizePreloadedArgIntrin(), legalizeRsqClampIntrinsic(), legalizeSBufferLoad(), legalizeWaveID(), legalizeWorkitemIDIntrinsic(), llvm::AMDGPUAS::LOCAL_ADDRESS, llvm::SI::KernelInputOffsets::LOCAL_SIZE_X, llvm::SI::KernelInputOffsets::LOCAL_SIZE_Y, llvm::SI::KernelInputOffsets::LOCAL_SIZE_Z, MI, llvm::LegalizerHelper::MIRBuilder, MRI, llvm::SI::KernelInputOffsets::NGROUPS_X, llvm::SI::KernelInputOffsets::NGROUPS_Y, llvm::SI::KernelInputOffsets::NGROUPS_Z, llvm::LegalizerHelper::Observer, llvm::AMDGPUAS::PRIVATE_ADDRESS, llvm::AMDGPUFunctionArgInfo::QUEUE_PTR, S32, llvm::LLT::scalar(), llvm::MachineOperand::setMBB(), std::swap(), TRI, verifyCFIntrinsic(), llvm::AMDGPUFunctionArgInfo::WORKGROUP_ID_X, llvm::AMDGPUFunctionArgInfo::WORKGROUP_ID_Y, llvm::AMDGPUFunctionArgInfo::WORKGROUP_ID_Z, llvm::AMDGPUFunctionArgInfo::WORKITEM_ID_X, llvm::AMDGPUFunctionArgInfo::WORKITEM_ID_Y, and llvm::AMDGPUFunctionArgInfo::WORKITEM_ID_Z.

◆ legalizeIntrinsicTrunc()

| bool AMDGPULegalizerInfo::legalizeIntrinsicTrunc | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 2469 of file AMDGPULegalizerInfo.cpp.

References assert(), B, extractF64Exponent(), llvm::Hi, llvm::CmpInst::ICMP_SGT, llvm::CmpInst::ICMP_SLT, MI, MRI, S1, S32, S64, and llvm::LLT::scalar().

Referenced by legalizeCustom().

◆ legalizeIsAddrSpace()

| bool AMDGPULegalizerInfo::legalizeIsAddrSpace | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B, | ||

| unsigned | AddrSpace | ||

| ) | const |

Definition at line 5499 of file AMDGPULegalizerInfo.cpp.

References B, getSegmentAperture(), llvm::CmpInst::ICMP_EQ, MI, MRI, and llvm::LLT::scalar().

Referenced by legalizeIntrinsic().

◆ legalizeITOFP()

| bool AMDGPULegalizerInfo::legalizeITOFP | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B, | ||

| bool | Signed | ||

| ) | const |

Definition at line 2514 of file AMDGPULegalizerInfo.cpp.

References assert(), B, MI, MRI, S32, S64, llvm::LLT::scalar(), Signed, and X.

Referenced by legalizeCustom().

◆ legalizeKernargMemParameter()

| bool AMDGPULegalizerInfo::legalizeKernargMemParameter | ( | MachineInstr & | MI, |

| MachineIRBuilder & | B, | ||

| uint64_t | Offset, | ||

| Align | Alignment = Align(4) |

||

| ) | const |

Legalize a value that's loaded from kernel arguments.

This is only used by legacy intrinsics.

Definition at line 4371 of file AMDGPULegalizerInfo.cpp.

References assert(), B, llvm::AMDGPUAS::CONSTANT_ADDRESS, getKernargParameterPtr(), MI, llvm::MachineMemOperand::MODereferenceable, llvm::MachineMemOperand::MOInvariant, llvm::Offset, Ptr, and llvm::LLT::scalar().

Referenced by legalizeIntrinsic().

◆ legalizeLDSKernelId()

| bool AMDGPULegalizerInfo::legalizeLDSKernelId | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 5481 of file AMDGPULegalizerInfo.cpp.

References B, getLDSKernelId(), llvm::AMDGPUMachineFunction::isEntryFunction(), llvm::AMDGPUFunctionArgInfo::LDS_KERNEL_ID, legalizePreloadedArgIntrin(), MI, and MRI.

◆ legalizeLoad()

| bool AMDGPULegalizerInfo::legalizeLoad | ( | LegalizerHelper & | Helper, |

| MachineInstr & | MI | ||

| ) | const |

Definition at line 3023 of file AMDGPULegalizerInfo.cpp.

References B, castBufferRsrcFromV4I32(), llvm::GISelChangeObserver::changedInstr(), llvm::GISelChangeObserver::changingInstr(), llvm::AMDGPUAS::CONSTANT_ADDRESS, llvm::AMDGPUAS::CONSTANT_ADDRESS_32BIT, llvm::LLT::getAddressSpace(), llvm::MachineMemOperand::getAlign(), llvm::MachineFunction::getMachineMemOperand(), llvm::MachineMemOperand::getMemoryType(), llvm::LLT::getSizeInBits(), hasBufferRsrcWorkaround(), isRegisterType(), llvm::LLT::isVector(), MI, llvm::LegalizerHelper::MIRBuilder, MRI, llvm::LegalizerHelper::Observer, llvm::LLT::pointer(), llvm::PowerOf2Ceil(), shouldWidenLoad(), llvm::Align::value(), and widenToNextPowerOf2().

Referenced by legalizeCustom().

◆ legalizeMinNumMaxNum()

| bool AMDGPULegalizerInfo::legalizeMinNumMaxNum | ( | LegalizerHelper & | Helper, |

| MachineInstr & | MI | ||

| ) | const |

Definition at line 2641 of file AMDGPULegalizerInfo.cpp.

References llvm::MachineFunction::getInfo(), llvm::MachineIRBuilder::getMF(), llvm::SIMachineFunctionInfo::getMode(), llvm::SIModeRegisterDefaults::IEEE, llvm::LegalizerHelper::Legalized, llvm::LegalizerHelper::lowerFMinNumMaxNum(), MI, and llvm::LegalizerHelper::MIRBuilder.

Referenced by legalizeCustom().

◆ legalizeMul()

| bool AMDGPULegalizerInfo::legalizeMul | ( | LegalizerHelper & | Helper, |

| MachineInstr & | MI | ||

| ) | const |

Definition at line 4079 of file AMDGPULegalizerInfo.cpp.

References assert(), B, buildMultiply(), llvm::GCNSubtarget::getGeneration(), llvm::LLT::getSizeInBits(), llvm::AMDGPUSubtarget::GFX10, llvm::GCNSubtarget::hasFullRate64Ops(), llvm::GCNSubtarget::hasMad64_32(), llvm::LLT::isScalar(), MI, llvm::LegalizerHelper::MIRBuilder, MRI, llvm::SmallVectorTemplateBase< T, bool >::push_back(), S32, llvm::LLT::scalar(), and Size.

Referenced by legalizeCustom().

◆ legalizePointerAsRsrcIntrin()

| bool AMDGPULegalizerInfo::legalizePointerAsRsrcIntrin | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

To create a buffer resource from a 64-bit pointer, mask off the upper 32 bits of the pointer and replace them with the stride argument, then merge_values everything together.

In the common case of a raw buffer (the stride component is 0), we can just AND off the upper half.

Definition at line 5413 of file AMDGPULegalizerInfo.cpp.

References B, llvm::getIConstantVRegValWithLookThrough(), llvm::MachineInstrBuilder::getReg(), MI, MRI, S32, and llvm::LLT::scalar().

Referenced by legalizeIntrinsic().

◆ legalizePreloadedArgIntrin()

| bool AMDGPULegalizerInfo::legalizePreloadedArgIntrin | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B, | ||

| AMDGPUFunctionArgInfo::PreloadedValue | ArgType | ||

| ) | const |

Definition at line 4296 of file AMDGPULegalizerInfo.cpp.

References B, loadInputValue(), and MI.

Referenced by legalizeImplicitArgPtr(), legalizeIntrinsic(), and legalizeLDSKernelId().

◆ legalizeRsqClampIntrinsic()

| bool AMDGPULegalizerInfo::legalizeRsqClampIntrinsic | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 5316 of file AMDGPULegalizerInfo.cpp.

References B, llvm::GCNSubtarget::getGeneration(), llvm::APFloat::getLargest(), llvm::SIMachineFunctionInfo::getMode(), llvm::SIModeRegisterDefaults::IEEE, llvm::APFloatBase::IEEEdouble(), llvm::APFloatBase::IEEEsingle(), MI, MRI, llvm::LLT::scalar(), and llvm::AMDGPUSubtarget::VOLCANIC_ISLANDS.

Referenced by legalizeIntrinsic().

◆ legalizeSBufferLoad()

| bool AMDGPULegalizerInfo::legalizeSBufferLoad | ( | LegalizerHelper & | Helper, |

| MachineInstr & | MI | ||

| ) | const |

Definition at line 6555 of file AMDGPULegalizerInfo.cpp.

References assert(), B, llvm::LegalizerHelper::bitcastDst(), castBufferRsrcFromV4I32(), llvm::GISelChangeObserver::changedInstr(), llvm::GISelChangeObserver::changingInstr(), getBitcastRegisterType(), llvm::MachineFunction::getMachineMemOperand(), getPow2ScalarType(), getPow2VectorType(), llvm::LLT::getSizeInBits(), hasBufferRsrcWorkaround(), llvm::GCNSubtarget::hasScalarDwordx3Loads(), llvm::GCNSubtarget::hasScalarSubwordLoads(), llvm::isPowerOf2_32(), llvm::LLT::isVector(), MI, llvm::LegalizerHelper::MIRBuilder, llvm::MachineMemOperand::MODereferenceable, llvm::MachineMemOperand::MOInvariant, llvm::MachineMemOperand::MOLoad, llvm::LegalizerHelper::moreElementsVectorDst(), llvm::LegalizerHelper::Observer, llvm::LLT::scalar(), shouldBitcastLoadStoreType(), Size, and llvm::LegalizerHelper::widenScalarDst().

Referenced by legalizeIntrinsic().

◆ legalizeSetFPEnv()

| bool AMDGPULegalizerInfo::legalizeSetFPEnv | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 6993 of file AMDGPULegalizerInfo.cpp.

References B, FPEnvModeBitField, FPEnvTrapBitField, MI, MRI, S32, and S64.

Referenced by legalizeCustom().

◆ legalizeSignedDIV_REM()

| bool AMDGPULegalizerInfo::legalizeSignedDIV_REM | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 4648 of file AMDGPULegalizerInfo.cpp.

References B, llvm::LLT::getSizeInBits(), legalizeUnsignedDIV_REM32Impl(), legalizeUnsignedDIV_REM64Impl(), LHS, llvm_unreachable, MI, MRI, RHS, S32, S64, and llvm::LLT::scalar().

Referenced by legalizeCustom().

◆ legalizeSinCos()

| bool AMDGPULegalizerInfo::legalizeSinCos | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 2772 of file AMDGPULegalizerInfo.cpp.

References B, llvm::AMDGPUSubtarget::hasTrigReducedRange(), llvm::numbers::inv_pi, MI, and MRI.

Referenced by legalizeCustom().

◆ legalizeStackSave()

| bool AMDGPULegalizerInfo::legalizeStackSave | ( | MachineInstr & | MI, |

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 6942 of file AMDGPULegalizerInfo.cpp.

References B, llvm::TargetLoweringBase::getStackPointerRegisterToSaveRestore(), llvm::GCNSubtarget::getTargetLowering(), and MI.

Referenced by legalizeCustom().

◆ legalizeStore()

| bool AMDGPULegalizerInfo::legalizeStore | ( | LegalizerHelper & | Helper, |

| MachineInstr & | MI | ||

| ) | const |

Definition at line 3112 of file AMDGPULegalizerInfo.cpp.

References B, castBufferRsrcArgToV4I32(), llvm::GISelChangeObserver::changedInstr(), llvm::GISelChangeObserver::changingInstr(), hasBufferRsrcWorkaround(), MI, llvm::LegalizerHelper::MIRBuilder, MRI, and llvm::LegalizerHelper::Observer.

Referenced by legalizeCustom().

◆ legalizeTrap()

| bool AMDGPULegalizerInfo::legalizeTrap | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 6628 of file AMDGPULegalizerInfo.cpp.

References llvm::GCNSubtarget::AMDHSA, B, llvm::GCNSubtarget::getTrapHandlerAbi(), llvm::GCNSubtarget::isTrapHandlerEnabled(), legalizeTrapEndpgm(), legalizeTrapHsa(), legalizeTrapHsaQueuePtr(), MI, MRI, and llvm::GCNSubtarget::supportsGetDoorbellID().

Referenced by legalizeCustom().

◆ legalizeTrapEndpgm()

| bool AMDGPULegalizerInfo::legalizeTrapEndpgm | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 6639 of file AMDGPULegalizerInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMBB(), llvm::MachineBasicBlock::addSuccessor(), B, llvm::BuildMI(), llvm::MachineFunction::CreateMachineBasicBlock(), DL, llvm::MachineBasicBlock::end(), llvm::MachineBasicBlock::getParent(), MI, llvm::MachineFunction::push_back(), llvm::MachineBasicBlock::splitAt(), and llvm::MachineBasicBlock::succ_empty().

Referenced by legalizeTrap().

◆ legalizeTrapHsa()

| bool AMDGPULegalizerInfo::legalizeTrapHsa | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 6728 of file AMDGPULegalizerInfo.cpp.

References B, llvm::GCNSubtarget::getInstrInfo(), llvm::GCNSubtarget::hasPrivEnabledTrap2NopBug(), llvm::SIInstrInfo::insertSimulatedTrap(), llvm::GCNSubtarget::LLVMAMDHSATrap, MI, and MRI.

Referenced by legalizeTrap().

◆ legalizeTrapHsaQueuePtr()

| bool AMDGPULegalizerInfo::legalizeTrapHsaQueuePtr | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 6668 of file AMDGPULegalizerInfo.cpp.

References llvm::AMDGPU::AMDHSA_COV5, B, llvm::commonAlignment(), llvm::AMDGPUAS::CONSTANT_ADDRESS, llvm::AMDGPU::getAMDHSACodeObjectVersion(), llvm::MachineFunction::getFunction(), llvm::AMDGPUTargetLowering::getImplicitParameterOffset(), llvm::MachineFunction::getMachineMemOperand(), llvm::GlobalValue::getParent(), llvm::GCNSubtarget::getTargetLowering(), llvm::RegState::Implicit, llvm::AMDGPUFunctionArgInfo::KERNARG_SEGMENT_PTR, llvm::GCNSubtarget::LLVMAMDHSATrap, loadInputValue(), MI, llvm::MachineMemOperand::MODereferenceable, llvm::MachineMemOperand::MOInvariant, llvm::MachineMemOperand::MOLoad, MRI, llvm::Offset, llvm::LLT::pointer(), llvm::AMDGPUFunctionArgInfo::QUEUE_PTR, llvm::AMDGPUTargetLowering::QUEUE_PTR, S64, and llvm::LLT::scalar().

Referenced by legalizeTrap().

◆ legalizeUnsignedDIV_REM()

| bool AMDGPULegalizerInfo::legalizeUnsignedDIV_REM | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 4608 of file AMDGPULegalizerInfo.cpp.

References B, legalizeUnsignedDIV_REM32Impl(), legalizeUnsignedDIV_REM64Impl(), llvm_unreachable, MI, MRI, S32, S64, and llvm::LLT::scalar().

Referenced by legalizeCustom().

◆ legalizeUnsignedDIV_REM32Impl()

| void AMDGPULegalizerInfo::legalizeUnsignedDIV_REM32Impl | ( | MachineIRBuilder & | B, |

| Register | DstDivReg, | ||

| Register | DstRemReg, | ||

| Register | Num, | ||

| Register | Den | ||

| ) | const |

Definition at line 4408 of file AMDGPULegalizerInfo.cpp.

References B, Cond, llvm::CmpInst::ICMP_UGE, S1, S32, llvm::LLT::scalar(), X, and Y.

Referenced by legalizeSignedDIV_REM(), and legalizeUnsignedDIV_REM().

◆ legalizeUnsignedDIV_REM64Impl()

| void AMDGPULegalizerInfo::legalizeUnsignedDIV_REM64Impl | ( | MachineIRBuilder & | B, |

| Register | DstDivReg, | ||

| Register | DstRemReg, | ||

| Register | Num, | ||

| Register | Den | ||

| ) | const |

Definition at line 4496 of file AMDGPULegalizerInfo.cpp.

References B, emitReciprocalU64(), llvm::CmpInst::ICMP_EQ, llvm::CmpInst::ICMP_NE, llvm::CmpInst::ICMP_UGE, S1, S32, S64, and llvm::LLT::scalar().

Referenced by legalizeSignedDIV_REM(), and legalizeUnsignedDIV_REM().

◆ legalizeWaveID()

| bool AMDGPULegalizerInfo::legalizeWaveID | ( | MachineInstr & | MI, |

| MachineIRBuilder & | B | ||

| ) | const |

Definition at line 6952 of file AMDGPULegalizerInfo.cpp.

References B, llvm::GCNSubtarget::hasArchitectedSGPRs(), MI, S32, and llvm::LLT::scalar().

Referenced by legalizeIntrinsic().

◆ legalizeWorkitemIDIntrinsic()

| bool AMDGPULegalizerInfo::legalizeWorkitemIDIntrinsic | ( | MachineInstr & | MI, |

| MachineRegisterInfo & | MRI, | ||

| MachineIRBuilder & | B, | ||

| unsigned | Dim, | ||

| AMDGPUFunctionArgInfo::PreloadedValue | ArgType | ||

| ) | const |

Definition at line 4313 of file AMDGPULegalizerInfo.cpp.

References B, llvm::bit_width(), llvm::AMDGPUSubtarget::getMaxWorkitemID(), llvm::SIMachineFunctionInfo::getPreloadedValue(), loadInputValue(), llvm::CallingConv::MaxID, MI, MRI, replaceWithConstant(), and llvm::LLT::scalar().

Referenced by legalizeIntrinsic().

◆ loadInputValue() [1/2]

| bool AMDGPULegalizerInfo::loadInputValue | ( | Register | DstReg, |

| MachineIRBuilder & | B, | ||

| AMDGPUFunctionArgInfo::PreloadedValue | ArgType | ||

| ) | const |

Definition at line 4232 of file AMDGPULegalizerInfo.cpp.

References llvm::CallingConv::AMDGPU_Gfx, B, CC, llvm::ArgDescriptor::createRegister(), llvm::SIMachineFunctionInfo::getPreloadedValue(), llvm::GCNSubtarget::hasArchitectedSGPRs(), llvm::SIMachineFunctionInfo::hasWorkGroupIDZ(), llvm::AMDGPU::isCompute(), llvm::AMDGPU::isEntryFunctionCC(), llvm::AMDGPUFunctionArgInfo::KERNARG_SEGMENT_PTR, loadInputValue(), llvm::LLT::scalar(), llvm::AMDGPUFunctionArgInfo::WORKGROUP_ID_X, llvm::AMDGPUFunctionArgInfo::WORKGROUP_ID_Y, and llvm::AMDGPUFunctionArgInfo::WORKGROUP_ID_Z.

◆ loadInputValue() [2/2]

| bool AMDGPULegalizerInfo::loadInputValue | ( | Register | DstReg, |

| MachineIRBuilder & | B, | ||

| const ArgDescriptor * | Arg, | ||

| const TargetRegisterClass * | ArgRC, | ||

| LLT | ArgTy | ||

| ) | const |

Definition at line 4199 of file AMDGPULegalizerInfo.cpp.

References assert(), B, llvm::getFunctionLiveInPhysReg(), llvm::ArgDescriptor::getMask(), llvm::ArgDescriptor::getRegister(), llvm::ArgDescriptor::isMasked(), llvm::Register::isPhysicalRegister(), llvm::Register::isVirtual(), S32, and llvm::LLT::scalar().

Referenced by getImplicitArgPtr(), getKernargParameterPtr(), getSegmentAperture(), legalizePreloadedArgIntrin(), legalizeTrapHsaQueuePtr(), legalizeWorkitemIDIntrinsic(), and loadInputValue().

◆ splitBufferOffsets()

| std::pair< Register, unsigned > AMDGPULegalizerInfo::splitBufferOffsets | ( | MachineIRBuilder & | B, |

| Register | OrigOffset | ||

| ) | const |

Definition at line 5519 of file AMDGPULegalizerInfo.cpp.

References B, llvm::AMDGPU::getBaseWithConstantOffset(), llvm::SIInstrInfo::getMaxMUBUFImmOffset(), MRI, S32, and llvm::LLT::scalar().

Referenced by legalizeBufferAtomic(), legalizeBufferLoad(), and legalizeBufferStore().

The documentation for this class was generated from the following files:

- lib/Target/AMDGPU/AMDGPULegalizerInfo.h

- lib/Target/AMDGPU/AMDGPULegalizerInfo.cpp

Public Member Functions inherited from

Public Member Functions inherited from