#include "Target/AMDGPU/SIRegisterInfo.h"

Classes | |

| struct | SpilledReg |

Static Public Member Functions | |

| static unsigned | getSubRegFromChannel (unsigned Channel, unsigned NumRegs=1) |

| static bool | isChainScratchRegister (Register VGPR) |

| static LLVM_READONLY const TargetRegisterClass * | getSGPRClassForBitWidth (unsigned BitWidth) |

| static bool | isSGPRClass (const TargetRegisterClass *RC) |

| static bool | isVGPRClass (const TargetRegisterClass *RC) |

| static bool | isAGPRClass (const TargetRegisterClass *RC) |

| static bool | hasVGPRs (const TargetRegisterClass *RC) |

| static bool | hasAGPRs (const TargetRegisterClass *RC) |

| static bool | hasSGPRs (const TargetRegisterClass *RC) |

| static bool | hasVectorRegisters (const TargetRegisterClass *RC) |

| static unsigned | getNumCoveredRegs (LaneBitmask LM) |

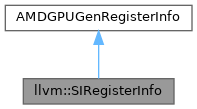

Detailed Description

Definition at line 32 of file SIRegisterInfo.h.

Constructor & Destructor Documentation

◆ SIRegisterInfo()

| SIRegisterInfo::SIRegisterInfo | ( | const GCNSubtarget & | ST | ) |

Definition at line 320 of file SIRegisterInfo.cpp.

References assert(), llvm::call_once(), llvm::MCRegister::from(), Idx, llvm::AMDGPU::isHi(), llvm::Offset, llvm::BitVector::resize(), llvm::BitVector::set(), llvm::size(), Size, and SubRegFromChannelTableWidthMap.

Member Function Documentation

◆ buildSpillLoadStore()

| void SIRegisterInfo::buildSpillLoadStore | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MI, | ||

| const DebugLoc & | DL, | ||

| unsigned | LoadStoreOp, | ||

| int | Index, | ||

| Register | ValueReg, | ||

| bool | ValueIsKill, | ||

| MCRegister | ScratchOffsetReg, | ||

| int64_t | InstrOffset, | ||

| MachineMemOperand * | MMO, | ||

| RegScavenger * | RS, | ||

| LiveRegUnits * | LiveUnits = nullptr |

||

| ) | const |

Definition at line 1329 of file SIRegisterInfo.cpp.

References llvm::Add, llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), assert(), llvm::LiveRegUnits::available(), llvm::BuildMI(), llvm::commonAlignment(), DL, llvm::MachineBasicBlock::end(), llvm::SIInstrFlags::FlatScratch, llvm::GCNSubtarget::getConstantBusLimit(), llvm::getDefRegState(), llvm::MachineMemOperand::getFlags(), llvm::AMDGPU::getFlatScratchInstSTfromSS(), llvm::AMDGPU::getFlatScratchInstSVfromSS(), getFlatScratchSpillOpcode(), llvm::MachineFunction::getFrameInfo(), llvm::MachineFunction::getInfo(), llvm::GCNSubtarget::getInstrInfo(), llvm::getKillRegState(), llvm::MachineFunction::getMachineMemOperand(), llvm::AMDGPU::getNamedOperandIdx(), llvm::MachineFrameInfo::getObjectAlign(), llvm::MachineFrameInfo::getObjectOffset(), getOffenMUBUFLoad(), getOffenMUBUFStore(), llvm::MachineBasicBlock::getParent(), llvm::MachineMemOperand::getPointerInfo(), llvm::AMDGPU::getRegBitWidth(), getRegClassForReg(), llvm::MachineFunction::getRegInfo(), llvm::SIMachineFunctionInfo::getScratchRSrcReg(), llvm::SIMachineFunctionInfo::getStackPtrOffsetReg(), getSubRegFromChannel(), llvm::SIMachineFunctionInfo::getVGPRForAGPRCopy(), llvm::AMDGPUSubtarget::getWavefrontSize(), llvm::MachinePointerInfo::getWithOffset(), llvm::GCNSubtarget::hasFlatScratchSTMode(), llvm::GCNSubtarget::hasGFX90AInsts(), llvm::RegState::Implicit, llvm::RegState::ImplicitDefine, isAGPRClass(), llvm::AMDGPUMachineFunction::isBottomOfStack(), llvm::RegScavenger::isRegUsed(), llvm::MachineRegisterInfo::isReserved(), llvm::RegState::Kill, MBB, MI, llvm::MOLastUse, llvm::Offset, llvm::AMDGPUAS::PRIVATE_ADDRESS, llvm::MachineInstr::ReloadReuse, llvm::report_fatal_error(), llvm::RegScavenger::scavengeRegisterBackwards(), llvm::MachineInstr::setAsmPrinterFlag(), llvm::RegScavenger::setRegUsed(), Size, spillVGPRtoAGPR(), SubReg, llvm::AMDGPU::CPol::TH_LU, and TII.

Referenced by buildVGPRSpillLoadStore(), and eliminateFrameIndex().

◆ buildVGPRSpillLoadStore()

| void SIRegisterInfo::buildVGPRSpillLoadStore | ( | SGPRSpillBuilder & | SB, |

| int | Index, | ||

| int | Offset, | ||

| bool | IsLoad, | ||

| bool | IsKill = true |

||

| ) | const |

Definition at line 1727 of file SIRegisterInfo.cpp.

References llvm::SIMachineFunctionInfo::addToSpilledVGPRs(), assert(), buildSpillLoadStore(), llvm::SGPRSpillBuilder::DL, llvm::SGPRSpillBuilder::EltSize, llvm::GCNSubtarget::enableFlatScratch(), getBaseRegister(), llvm::MachinePointerInfo::getFixedStack(), llvm::MachineFunction::getFrameInfo(), getFrameRegister(), llvm::MachineFunction::getMachineMemOperand(), llvm::MachineFrameInfo::getObjectAlign(), llvm::MachineFrameInfo::getStackID(), hasBasePointer(), llvm::MachineFrameInfo::isFixedObjectIndex(), llvm::SGPRSpillBuilder::MBB, llvm::SGPRSpillBuilder::MF, llvm::SGPRSpillBuilder::MFI, llvm::SGPRSpillBuilder::MI, llvm::MachineMemOperand::MOLoad, llvm::MachineMemOperand::MOStore, llvm::Offset, llvm::SGPRSpillBuilder::RS, llvm::TargetStackID::SGPRSpill, and llvm::SGPRSpillBuilder::TmpVGPR.

Referenced by llvm::SGPRSpillBuilder::prepare(), llvm::SGPRSpillBuilder::readWriteTmpVGPR(), and llvm::SGPRSpillBuilder::restore().

◆ eliminateFrameIndex()

|

override |

Definition at line 2074 of file SIRegisterInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::SIMachineFunctionInfo::addToSpilledVGPRs(), assert(), llvm::BuildMI(), buildMUBUFOffsetLoadStore(), buildSpillLoadStore(), llvm::MachineOperand::ChangeToImmediate(), llvm::MachineOperand::ChangeToRegister(), DL, llvm::GCNSubtarget::enableFlatScratch(), llvm::SIInstrFlags::FlatScratch, getBaseRegister(), llvm::AMDGPU::getFlatScratchInstSTfromSS(), llvm::AMDGPU::getFlatScratchInstSVfromSVS(), llvm::MachineFunction::getFrameInfo(), getFrameRegister(), llvm::MachineOperand::getImm(), llvm::MachineFunction::getInfo(), llvm::GCNSubtarget::getInstrInfo(), llvm::AMDGPU::getNamedOperandIdx(), getNumSubRegsForSpillOp(), llvm::MachineInstr::getOpcode(), llvm::MachineOperand::getReg(), llvm::MachineInstrBuilder::getReg(), llvm::SIMachineFunctionInfo::getSGPRForEXECCopy(), llvm::SIMachineFunctionInfo::getStackPtrOffsetReg(), llvm::AMDGPUSubtarget::getWavefrontSizeLog2(), hasBasePointer(), llvm::GCNSubtarget::hasFlatScratchSTMode(), llvm::AMDGPUSubtarget::hasInv2PiInlineImm(), llvm::AMDGPU::hasNamedOperand(), I, llvm::AMDGPUMachineFunction::isBottomOfStack(), llvm::AMDGPU::isInlinableLiteral32(), llvm::MachineOperand::isKill(), llvm::RegScavenger::isRegUsed(), isSGPRClass(), llvm::Register::isValid(), llvm::RegState::Kill, MBB, MI, llvm::Offset, llvm::AMDGPUAS::PRIVATE_ADDRESS, llvm::report_fatal_error(), restoreSGPR(), llvm::RegScavenger::scavengeRegisterBackwards(), llvm::MachineOperand::setImm(), llvm::MachineOperand::setIsKill(), llvm::MachineOperand::setReg(), spillSGPR(), and TII.

◆ eliminateSGPRToVGPRSpillFrameIndex()

| bool SIRegisterInfo::eliminateSGPRToVGPRSpillFrameIndex | ( | MachineBasicBlock::iterator | MI, |

| int | FI, | ||

| RegScavenger * | RS, | ||

| SlotIndexes * | Indexes = nullptr, |

||

| LiveIntervals * | LIS = nullptr, |

||

| bool | SpillToPhysVGPRLane = false |

||

| ) | const |

Special case of eliminateFrameIndex.

Returns true if the SGPR was spilled to a VGPR and the stack slot can be safely eliminated when all other users are handled.

Definition at line 2035 of file SIRegisterInfo.cpp.

References llvm_unreachable, MI, restoreSGPR(), and spillSGPR().

◆ findReachingDef()

| MachineInstr * SIRegisterInfo::findReachingDef | ( | Register | Reg, |

| unsigned | SubReg, | ||

| MachineInstr & | Use, | ||

| MachineRegisterInfo & | MRI, | ||

| LiveIntervals * | LIS | ||

| ) | const |

Definition at line 3152 of file SIRegisterInfo.cpp.

References assert(), llvm::Pass::getAnalysis(), llvm::LiveIntervals::getInstructionFromIndex(), llvm::LiveIntervals::getInstructionIndex(), llvm::LiveIntervals::getInterval(), llvm::LiveIntervals::getRegUnit(), llvm::LiveRange::getVNInfoAt(), llvm::LiveIntervals::hasInterval(), llvm::LiveInterval::hasSubRanges(), llvm::SlotIndex::isValid(), MRI, llvm::LiveInterval::subranges(), and SubReg.

◆ findUnusedRegister()

| MCRegister SIRegisterInfo::findUnusedRegister | ( | const MachineRegisterInfo & | MRI, |

| const TargetRegisterClass * | RC, | ||

| const MachineFunction & | MF, | ||

| bool | ReserveHighestRegister = false |

||

| ) | const |

Returns a lowest register that is not used at any point in the function.

If all registers are used, then this function will return AMDGPU::NoRegister. If ReserveHighestRegister = true, then return highest unused register.

Definition at line 2955 of file SIRegisterInfo.cpp.

References MRI, and llvm::reverse().

◆ get32BitRegister()

Definition at line 3205 of file SIRegisterInfo.cpp.

References assert().

Referenced by llvm::SIInstrInfo::copyPhysReg(), and llvm::SIInstrInfo::foldImmediate().

◆ getAGPRClassForBitWidth()

| const TargetRegisterClass * SIRegisterInfo::getAGPRClassForBitWidth | ( | unsigned | BitWidth | ) | const |

Definition at line 2748 of file SIRegisterInfo.cpp.

References llvm::BitWidth, getAlignedAGPRClassForBitWidth(), getAnyAGPRClassForBitWidth(), and llvm::GCNSubtarget::needsAlignedVGPRs().

Referenced by getEquivalentAGPRClass(), getRegClassForSizeOnBank(), and isProperlyAlignedRC().

◆ getAlignedHighSGPRForRC()

| MCRegister SIRegisterInfo::getAlignedHighSGPRForRC | ( | const MachineFunction & | MF, |

| const unsigned | Align, | ||

| const TargetRegisterClass * | RC | ||

| ) | const |

Return the largest available SGPR aligned to Align for the register class RC.

Definition at line 551 of file SIRegisterInfo.cpp.

References llvm::alignDown(), and llvm::GCNSubtarget::getMaxNumSGPRs().

Referenced by reservedPrivateSegmentBufferReg().

◆ getAllAGPRRegMask()

Definition at line 529 of file SIRegisterInfo.cpp.

◆ getAllAllocatableSRegMask()

Definition at line 537 of file SIRegisterInfo.cpp.

◆ getAllSGPR128()

| ArrayRef< MCPhysReg > SIRegisterInfo::getAllSGPR128 | ( | const MachineFunction & | MF | ) | const |

Return all SGPR128 which satisfy the waves per execution unit requirement of the subtarget.

Definition at line 3257 of file SIRegisterInfo.cpp.

References llvm::GCNSubtarget::getMaxNumSGPRs().

◆ getAllSGPR32()

| ArrayRef< MCPhysReg > SIRegisterInfo::getAllSGPR32 | ( | const MachineFunction & | MF | ) | const |

Return all SGPR32 which satisfy the waves per execution unit requirement of the subtarget.

Definition at line 3267 of file SIRegisterInfo.cpp.

References llvm::GCNSubtarget::getMaxNumSGPRs().

◆ getAllSGPR64()

| ArrayRef< MCPhysReg > SIRegisterInfo::getAllSGPR64 | ( | const MachineFunction & | MF | ) | const |

Return all SGPR64 which satisfy the waves per execution unit requirement of the subtarget.

Definition at line 3262 of file SIRegisterInfo.cpp.

References llvm::GCNSubtarget::getMaxNumSGPRs().

◆ getAllVectorRegMask()

Definition at line 533 of file SIRegisterInfo.cpp.

◆ getAllVGPRRegMask()

Definition at line 525 of file SIRegisterInfo.cpp.

◆ getBaseRegister()

| Register SIRegisterInfo::getBaseRegister | ( | ) | const |

Definition at line 523 of file SIRegisterInfo.cpp.

Referenced by buildVGPRSpillLoadStore(), eliminateFrameIndex(), and getReservedRegs().

◆ getBoolRC()

|

inline |

Definition at line 345 of file SIRegisterInfo.h.

Referenced by llvm::SIInstrInfo::convertNonUniformIfRegion(), llvm::SIInstrInfo::convertNonUniformLoopRegion(), llvm::SIInstrInfo::getAddNoCarry(), llvm::GCNSubtarget::getBoolRC(), getRegClass(), llvm::SIInstrInfo::insertEQ(), llvm::SIInstrInfo::insertNE(), and llvm::SIInstrInfo::insertVectorSelect().

◆ getCalleeSavedRegs()

|

override |

Definition at line 391 of file SIRegisterInfo.cpp.

References llvm::CallingConv::AMDGPU_CS_ChainPreserve, llvm::CallingConv::AMDGPU_Gfx, llvm::CallingConv::C, CC, llvm::CallingConv::Cold, llvm::CallingConv::Fast, llvm::Function::getCallingConv(), llvm::MachineFunction::getFunction(), and llvm::GCNSubtarget::hasGFX90AInsts().

◆ getCalleeSavedRegsViaCopy()

| const MCPhysReg * SIRegisterInfo::getCalleeSavedRegsViaCopy | ( | const MachineFunction * | MF | ) | const |

Definition at line 414 of file SIRegisterInfo.cpp.

◆ getCallPreservedMask()

|

override |

Definition at line 418 of file SIRegisterInfo.cpp.

References llvm::CallingConv::AMDGPU_CS_Chain, llvm::CallingConv::AMDGPU_CS_ChainPreserve, llvm::CallingConv::AMDGPU_Gfx, llvm::CallingConv::C, CC, llvm::CallingConv::Cold, llvm::CallingConv::Fast, and llvm::GCNSubtarget::hasGFX90AInsts().

◆ getChannelFromSubReg()

Definition at line 388 of file SIRegisterInfo.h.

References SubReg.

Referenced by expandSGPRCopy(), and llvm::SIInstrInfo::verifyInstruction().

◆ getCompatibleSubRegClass()

| const TargetRegisterClass * SIRegisterInfo::getCompatibleSubRegClass | ( | const TargetRegisterClass * | SuperRC, |

| const TargetRegisterClass * | SubRC, | ||

| unsigned | SubIdx | ||

| ) | const |

Returns a register class which is compatible with SuperRC, such that a subregister exists with class SubRC with subregister index SubIdx.

If this is impossible (e.g., an unaligned subregister index within a register tuple), return null.

Definition at line 2903 of file SIRegisterInfo.cpp.

References llvm::TargetRegisterClass::hasSubClassEq().

Referenced by llvm::SIInstrInfo::verifyInstruction().

◆ getConstrainedRegClassForOperand()

|

override |

Definition at line 3110 of file SIRegisterInfo.cpp.

References llvm::PointerUnion< PTs >::dyn_cast(), llvm::MachineOperand::getReg(), getRegClassForTypeOnBank(), and MRI.

◆ getCrossCopyRegClass()

|

override |

Returns a legal register class to copy a register in the specified class to or from.

If it is possible to copy the register directly without using a cross register class copy, return the specified RC. Returns NULL if it is not possible to copy between two registers of the specified class.

Definition at line 950 of file SIRegisterInfo.cpp.

References getEquivalentVGPRClass(), getWaveMaskRegClass(), llvm::GCNSubtarget::hasGFX90AInsts(), and isAGPRClass().

◆ getCSRFirstUseCost()

|

inlineoverride |

Definition at line 102 of file SIRegisterInfo.h.

◆ getEquivalentAGPRClass()

| const TargetRegisterClass * SIRegisterInfo::getEquivalentAGPRClass | ( | const TargetRegisterClass * | SRC | ) | const |

- Returns

- An AGPR reg class with the same width as

SRC

Definition at line 2885 of file SIRegisterInfo.cpp.

References assert(), getAGPRClassForBitWidth(), and Size.

Referenced by llvm::SIInstrInfo::legalizeOperands().

◆ getEquivalentSGPRClass()

| const TargetRegisterClass * SIRegisterInfo::getEquivalentSGPRClass | ( | const TargetRegisterClass * | VRC | ) | const |

- Returns

- A SGPR reg class with the same width as

SRC

Definition at line 2893 of file SIRegisterInfo.cpp.

References assert(), getSGPRClassForBitWidth(), and Size.

Referenced by llvm::SIInstrInfo::readlaneVGPRToSGPR().

◆ getEquivalentVGPRClass()

| const TargetRegisterClass * SIRegisterInfo::getEquivalentVGPRClass | ( | const TargetRegisterClass * | SRC | ) | const |

- Returns

- A VGPR reg class with the same width as

SRC

Definition at line 2877 of file SIRegisterInfo.cpp.

References assert(), getVGPRClassForBitWidth(), and Size.

Referenced by getCrossCopyRegClass(), llvm::SIInstrInfo::legalizeOperands(), llvm::SIInstrInfo::legalizeOpWithMove(), llvm::SIInstrInfo::moveToVALUImpl(), and llvm::SIInstrInfo::readlaneVGPRToSGPR().

◆ getExec()

| MCRegister SIRegisterInfo::getExec | ( | ) | const |

Definition at line 3126 of file SIRegisterInfo.cpp.

◆ getFrameIndexInstrOffset()

|

override |

Definition at line 798 of file SIRegisterInfo.cpp.

References assert(), llvm::AMDGPU::getNamedOperandIdx(), getScratchInstrOffset(), Idx, llvm::SIInstrInfo::isFLATScratch(), llvm::SIInstrInfo::isMUBUF(), and MI.

◆ getFrameRegister()

|

override |

Definition at line 502 of file SIRegisterInfo.cpp.

References llvm::GCNSubtarget::getFrameLowering(), llvm::SIMachineFunctionInfo::getFrameOffsetReg(), llvm::MachineFunction::getInfo(), llvm::SIMachineFunctionInfo::getStackPtrOffsetReg(), llvm::SIFrameLowering::hasFP(), and llvm::AMDGPUMachineFunction::isBottomOfStack().

Referenced by buildVGPRSpillLoadStore(), eliminateFrameIndex(), and llvm::SIFrameLowering::getFrameIndexReference().

◆ getHWRegIndex()

|

inline |

Definition at line 180 of file SIRegisterInfo.h.

References Reg.

Referenced by llvm::SIInstrInfo::copyPhysReg(), getReservedRegs(), indirectCopyToAGPR(), and llvm::SIInstrInfo::verifyInstruction().

◆ getLargestLegalSuperClass()

|

override |

Definition at line 448 of file SIRegisterInfo.cpp.

References llvm::TargetRegisterInfo::getLargestLegalSuperClass(), llvm::GCNSubtarget::hasMAIInsts(), isAGPRClass(), and isVGPRClass().

Referenced by llvm::SIInstrInfo::isLegalRegOperand().

◆ getNoPreservedMask()

Definition at line 439 of file SIRegisterInfo.cpp.

◆ getNumChannelsFromSubReg()

Definition at line 393 of file SIRegisterInfo.h.

References getNumCoveredRegs(), and SubReg.

◆ getNumCoveredRegs()

|

inlinestatic |

Definition at line 377 of file SIRegisterInfo.h.

References llvm::LaneBitmask::getAsInteger(), and llvm::popcount().

Referenced by getNumChannelsFromSubReg(), and llvm::GCNRegPressure::inc().

◆ getPointerRegClass()

|

override |

Definition at line 941 of file SIRegisterInfo.cpp.

◆ getProperlyAlignedRC()

| const TargetRegisterClass * SIRegisterInfo::getProperlyAlignedRC | ( | const TargetRegisterClass * | RC | ) | const |

Definition at line 3238 of file SIRegisterInfo.cpp.

References getAlignedAGPRClassForBitWidth(), getAlignedVectorSuperClassForBitWidth(), getAlignedVGPRClassForBitWidth(), isAGPRClass(), isVectorSuperClass(), isVGPRClass(), llvm::GCNSubtarget::needsAlignedVGPRs(), and Size.

Referenced by adjustAllocatableRegClass().

◆ getRegAsmName()

|

override |

Definition at line 2599 of file SIRegisterInfo.cpp.

References llvm::AMDGPUInstPrinter::getRegisterName().

◆ getRegClass()

| const TargetRegisterClass * SIRegisterInfo::getRegClass | ( | unsigned | RCID | ) | const |

Definition at line 3137 of file SIRegisterInfo.cpp.

References getBoolRC().

Referenced by adjustAllocatableRegClass(), llvm::SIInstrInfo::foldImmediate(), llvm::SIInstrInfo::getOpSize(), llvm::SIInstrInfo::insertVectorSelect(), llvm::SIInstrInfo::isBufferSMRD(), llvm::SIInstrInfo::isLegalRegOperand(), llvm::SIInstrInfo::isOperandLegal(), isSGPRClassID(), llvm::SIInstrInfo::legalizeOperands(), llvm::SIInstrInfo::legalizeOpWithMove(), llvm::SIInstrInfo::moveToVALUImpl(), and llvm::SIInstrInfo::verifyInstruction().

◆ getRegClassAlignmentNumBits()

|

inline |

Definition at line 435 of file SIRegisterInfo.h.

References llvm::RegTupleAlignUnitsMask, and llvm::TargetRegisterClass::TSFlags.

Referenced by isRegClassAligned().

◆ getRegClassForOperandReg()

| const TargetRegisterClass * SIRegisterInfo::getRegClassForOperandReg | ( | const MachineRegisterInfo & | MRI, |

| const MachineOperand & | MO | ||

| ) | const |

Definition at line 3002 of file SIRegisterInfo.cpp.

References llvm::MachineOperand::getReg(), getRegClassForReg(), llvm::MachineOperand::getSubReg(), and MRI.

◆ getRegClassForReg()

| const TargetRegisterClass * SIRegisterInfo::getRegClassForReg | ( | const MachineRegisterInfo & | MRI, |

| Register | Reg | ||

| ) | const |

Definition at line 2996 of file SIRegisterInfo.cpp.

References MRI.

Referenced by buildSpillLoadStore(), getRegClassForOperandReg(), isAGPR(), llvm::SIInstrInfo::isBasicBlockPrologue(), isVGPR(), llvm::SIInstrInfo::legalizeGenericOperand(), llvm::SIInstrInfo::legalizeOperandsVOP3(), llvm::SIInstrInfo::moveToVALUImpl(), and llvm::SIInstrInfo::verifyInstruction().

◆ getRegClassForSizeOnBank()

| const TargetRegisterClass * SIRegisterInfo::getRegClassForSizeOnBank | ( | unsigned | Size, |

| const RegisterBank & | Bank | ||

| ) | const |

Definition at line 3090 of file SIRegisterInfo.cpp.

References assert(), getAGPRClassForBitWidth(), llvm::RegisterBank::getID(), getSGPRClassForBitWidth(), getVGPRClassForBitWidth(), llvm_unreachable, Size, and llvm::AMDGPUSubtarget::useRealTrue16Insts().

Referenced by getRegClassForTypeOnBank().

◆ getRegClassForTypeOnBank()

|

inline |

Definition at line 337 of file SIRegisterInfo.h.

References getRegClassForSizeOnBank(), and llvm::LLT::getSizeInBits().

Referenced by getConstrainedRegClassForOperand().

◆ getRegPressureLimit()

|

override |

Definition at line 3044 of file SIRegisterInfo.cpp.

References llvm::MachineFunction::getFunction(), llvm::TargetRegisterClass::getID(), llvm::MachineFunction::getInfo(), llvm::AMDGPUMachineFunction::getLDSSize(), llvm::GCNSubtarget::getMaxNumSGPRs(), llvm::GCNSubtarget::getMaxNumVGPRs(), and llvm::AMDGPUSubtarget::getOccupancyWithLocalMemSize().

Referenced by getRegPressureSetLimit(), and indirectCopyToAGPR().

◆ getRegPressureSetLimit()

|

override |

Definition at line 3061 of file SIRegisterInfo.cpp.

References getRegPressureLimit(), Idx, and llvm_unreachable.

◆ getRegSplitParts()

| ArrayRef< int16_t > SIRegisterInfo::getRegSplitParts | ( | const TargetRegisterClass * | RC, |

| unsigned | EltSize | ||

| ) | const |

Definition at line 2980 of file SIRegisterInfo.cpp.

References assert(), and llvm::AMDGPU::getRegBitWidth().

Referenced by llvm::SIInstrInfo::copyPhysReg(), expandSGPRCopy(), llvm::SIInstrInfo::materializeImmediate(), and llvm::SGPRSpillBuilder::SGPRSpillBuilder().

◆ getRegUnitPressureSets()

Definition at line 3075 of file SIRegisterInfo.cpp.

References llvm::Empty.

◆ getReservedRegs()

|

override |

Definition at line 564 of file SIRegisterInfo.cpp.

References assert(), llvm::divideCeil(), llvm::SIMachineFunctionInfo::getAGPRSpillVGPRs(), getBaseRegister(), llvm::SIMachineFunctionInfo::getFrameOffsetReg(), getHWRegIndex(), llvm::MachineFunction::getInfo(), llvm::SIMachineFunctionInfo::getLongBranchReservedReg(), llvm::GCNSubtarget::getMaxNumSGPRs(), llvm::GCNSubtarget::getMaxNumVGPRs(), llvm::SIMachineFunctionInfo::getScratchRSrcReg(), llvm::SIMachineFunctionInfo::getSGPRForEXECCopy(), llvm::SIMachineFunctionInfo::getStackPtrOffsetReg(), llvm::SIMachineFunctionInfo::getVGPRForAGPRCopy(), llvm::SIMachineFunctionInfo::getVGPRSpillAGPRs(), llvm::SIMachineFunctionInfo::getWWMReservedRegs(), hasBasePointer(), llvm::GCNSubtarget::hasGFX90AInsts(), llvm::GCNSubtarget::hasMAIInsts(), isAGPRClass(), isSGPRClass(), isVGPRClass(), llvm::Reserved, and llvm::SIMachineFunctionInfo::usesAGPRs().

◆ getReturnAddressReg()

| MCRegister SIRegisterInfo::getReturnAddressReg | ( | const MachineFunction & | MF | ) | const |

Definition at line 3084 of file SIRegisterInfo.cpp.

◆ getScratchInstrOffset()

| int64_t SIRegisterInfo::getScratchInstrOffset | ( | const MachineInstr * | MI | ) | const |

Definition at line 790 of file SIRegisterInfo.cpp.

References assert(), llvm::AMDGPU::getNamedOperandIdx(), llvm::SIInstrInfo::isFLATScratch(), llvm::SIInstrInfo::isMUBUF(), and MI.

Referenced by getFrameIndexInstrOffset(), isFrameOffsetLegal(), and needsFrameBaseReg().

◆ getSGPRClassForBitWidth()

|

static |

Definition at line 2831 of file SIRegisterInfo.cpp.

References llvm::BitWidth.

Referenced by getEquivalentSGPRClass(), getRegClassForSizeOnBank(), llvm::SITargetLowering::getRegForInlineAsmConstraint(), isIllegalRegisterType(), moreElementsToNextExistingRegClass(), and AMDGPUDAGToDAGISel::Select().

◆ getSubRegAlignmentNumBits()

| unsigned SIRegisterInfo::getSubRegAlignmentNumBits | ( | const TargetRegisterClass * | RC, |

| unsigned | SubReg | ||

| ) | const |

Definition at line 3272 of file SIRegisterInfo.cpp.

References llvm::HasAGPR, llvm::HasSGPR, llvm::HasVGPR, llvm::RegKindMask, SubReg, and llvm::TargetRegisterClass::TSFlags.

◆ getSubRegFromChannel()

- Returns

- the sub reg enum value for the given

Channel(e.g. getSubRegFromChannel(0) -> AMDGPU::sub0)

Definition at line 541 of file SIRegisterInfo.cpp.

References assert(), llvm::size(), and SubRegFromChannelTableWidthMap.

Referenced by llvm::SITargetLowering::AddMemOpInit(), buildRegSequence(), buildRegSequence32(), buildSpillLoadStore(), computeIndirectRegAndOffset(), expandSGPRCopy(), llvm::SIInstrInfo::readlaneVGPRToSGPR(), and AMDGPUDAGToDAGISel::SelectBuildVector().

◆ getVCC()

| MCRegister SIRegisterInfo::getVCC | ( | ) | const |

Definition at line 3122 of file SIRegisterInfo.cpp.

Referenced by llvm::SIInstrInfo::getAddNoCarry(), and llvm::SIInstrInfo::moveToVALUImpl().

◆ getVectorSuperClassForBitWidth()

| const TargetRegisterClass * SIRegisterInfo::getVectorSuperClassForBitWidth | ( | unsigned | BitWidth | ) | const |

Definition at line 2822 of file SIRegisterInfo.cpp.

References llvm::BitWidth, getAlignedVectorSuperClassForBitWidth(), getAnyVectorSuperClassForBitWidth(), and llvm::GCNSubtarget::needsAlignedVGPRs().

Referenced by isProperlyAlignedRC().

◆ getVGPR64Class()

| const TargetRegisterClass * SIRegisterInfo::getVGPR64Class | ( | ) | const |

Definition at line 3130 of file SIRegisterInfo.cpp.

References llvm::GCNSubtarget::needsAlignedVGPRs().

Referenced by llvm::SIInstrInfo::copyPhysReg().

◆ getVGPRClassForBitWidth()

| const TargetRegisterClass * SIRegisterInfo::getVGPRClassForBitWidth | ( | unsigned | BitWidth | ) | const |

Definition at line 2672 of file SIRegisterInfo.cpp.

References llvm::BitWidth, getAlignedVGPRClassForBitWidth(), getAnyVGPRClassForBitWidth(), and llvm::GCNSubtarget::needsAlignedVGPRs().

Referenced by getEquivalentVGPRClass(), getRegClassForSizeOnBank(), and isProperlyAlignedRC().

◆ getWaveMaskRegClass()

|

inline |

Definition at line 350 of file SIRegisterInfo.h.

Referenced by llvm::AMDGPURegisterBankInfo::executeInWaterfallLoop(), getCrossCopyRegClass(), and llvm::SIInstrInfo::moveToVALUImpl().

◆ hasAGPRs()

|

inlinestatic |

- Returns

- true if this class contains AGPR registers.

Definition at line 235 of file SIRegisterInfo.h.

References llvm::HasAGPR, and llvm::TargetRegisterClass::TSFlags.

Referenced by hasVectorRegisters(), isAGPRClass(), isSGPRClass(), isVectorSuperClass(), isVGPRClass(), isVSSuperClass(), llvm::SIInstrInfo::legalizeOperandsVOP3(), and llvm::SIInstrInfo::readlaneVGPRToSGPR().

◆ hasBasePointer()

| bool SIRegisterInfo::hasBasePointer | ( | const MachineFunction & | MF | ) | const |

Definition at line 516 of file SIRegisterInfo.cpp.

References llvm::MachineFunction::getFrameInfo(), llvm::MachineFrameInfo::getNumFixedObjects(), and shouldRealignStack().

Referenced by buildVGPRSpillLoadStore(), eliminateFrameIndex(), and getReservedRegs().

◆ hasSGPRs()

|

inlinestatic |

- Returns

- true if this class contains SGPR registers.

Definition at line 240 of file SIRegisterInfo.h.

References llvm::HasSGPR, and llvm::TargetRegisterClass::TSFlags.

Referenced by isAGPRClass(), isSGPRClass(), isVectorSuperClass(), isVGPRClass(), and isVSSuperClass().

◆ hasVectorRegisters()

|

inlinestatic |

- Returns

- true if this class contains any vector registers.

Definition at line 245 of file SIRegisterInfo.h.

References hasAGPRs(), and hasVGPRs().

Referenced by llvm::SIInstrInfo::legalizeOperands(), and llvm::SIInstrInfo::verifyInstruction().

◆ hasVGPRs()

|

inlinestatic |

- Returns

- true if this class contains VGPR registers.

Definition at line 230 of file SIRegisterInfo.h.

References llvm::HasVGPR, and llvm::TargetRegisterClass::TSFlags.

Referenced by llvm::SIInstrInfo::canInsertSelect(), llvm::SIInstrInfo::copyPhysReg(), llvm::SIInstrInfo::expandPostRAPseudo(), hasVectorRegisters(), isAGPRClass(), isSGPRClass(), isVectorSuperClass(), isVGPRClass(), isVSSuperClass(), llvm::SIInstrInfo::legalizeOperands(), and llvm::SIInstrInfo::verifyInstruction().

◆ isAGPR()

| bool SIRegisterInfo::isAGPR | ( | const MachineRegisterInfo & | MRI, |

| Register | Reg | ||

| ) | const |

Definition at line 3015 of file SIRegisterInfo.cpp.

References getRegClassForReg(), isAGPRClass(), and MRI.

Referenced by llvm::SIInstrInfo::enforceOperandRCAlignment(), llvm::SIInstrInfo::expandPostRAPseudo(), llvm::SIInstrInfo::foldImmediate(), llvm::SIInstrInfo::getVALUOp(), llvm::SIInstrInfo::isOperandLegal(), isVectorRegister(), llvm::SIInstrInfo::legalizeOperandsVOP2(), and llvm::SIInstrInfo::verifyInstruction().

◆ isAGPRClass()

|

inlinestatic |

- Returns

- true if this class contains only AGPR registers

Definition at line 215 of file SIRegisterInfo.h.

References hasAGPRs(), hasSGPRs(), and hasVGPRs().

Referenced by buildSpillLoadStore(), llvm::SIInstrInfo::copyPhysReg(), getCrossCopyRegClass(), getLargestLegalSuperClass(), llvm::SIInstrInfo::getMovOpcode(), getProperlyAlignedRC(), llvm::AMDGPURegisterBankInfo::getRegBankFromRegClass(), llvm::SITargetLowering::getRegForInlineAsmConstraint(), getReservedRegs(), isAGPR(), isProperlyAlignedRC(), llvm::SIInstrInfo::legalizeOperands(), and llvm::SIMachineFunctionInfo::usesAGPRs().

◆ isAsmClobberable()

|

override |

Definition at line 740 of file SIRegisterInfo.cpp.

References llvm::MachineFunction::getRegInfo(), and llvm::MachineRegisterInfo::isReserved().

◆ isChainScratchRegister()

Definition at line 443 of file SIRegisterInfo.cpp.

Referenced by llvm::SIMachineFunctionInfo::allocateWWMSpill().

◆ isDivergentRegClass()

|

inlineoverride |

Definition at line 305 of file SIRegisterInfo.h.

References isSGPRClass().

◆ isFrameOffsetLegal()

|

override |

Definition at line 925 of file SIRegisterInfo.cpp.

References llvm::SIInstrFlags::FlatScratch, llvm::GCNSubtarget::getInstrInfo(), getScratchInstrOffset(), llvm::SIInstrInfo::isFLATScratch(), llvm::SIInstrInfo::isMUBUF(), MI, llvm::Offset, llvm::AMDGPUAS::PRIVATE_ADDRESS, and TII.

◆ isProperlyAlignedRC()

| bool SIRegisterInfo::isProperlyAlignedRC | ( | const TargetRegisterClass & | RC | ) | const |

Definition at line 3222 of file SIRegisterInfo.cpp.

References getAGPRClassForBitWidth(), getVectorSuperClassForBitWidth(), getVGPRClassForBitWidth(), llvm::TargetRegisterClass::hasSuperClassEq(), isAGPRClass(), isVectorSuperClass(), isVGPRClass(), and llvm::GCNSubtarget::needsAlignedVGPRs().

Referenced by llvm::SIInstrInfo::copyPhysReg(), and llvm::SIInstrInfo::verifyInstruction().

◆ isRegClassAligned()

|

inline |

Definition at line 440 of file SIRegisterInfo.h.

References assert(), and getRegClassAlignmentNumBits().

◆ isSGPRClass()

|

inlinestatic |

- Returns

- true if this class contains only SGPR registers

Definition at line 198 of file SIRegisterInfo.h.

References hasAGPRs(), hasSGPRs(), and hasVGPRs().

Referenced by llvm::SIInstrInfo::canInsertSelect(), llvm::SIInstrInfo::copyPhysReg(), eliminateFrameIndex(), llvm::SIInstrInfo::foldImmediate(), llvm::SIInstrInfo::getInstructionUniformity(), llvm::SIInstrInfo::getMovOpcode(), llvm::AMDGPURegisterBankInfo::getRegBankFromRegClass(), llvm::SITargetLowering::getRegForInlineAsmConstraint(), getReservedRegs(), llvm::SIInstrInfo::isBasicBlockPrologue(), isDivergentRegClass(), llvm::SIInstrInfo::isSafeToSink(), isSGPRClassID(), isSGPRReg(), llvm::SIInstrInfo::legalizeGenericOperand(), llvm::SIInstrInfo::legalizeOperands(), llvm::SIInstrInfo::legalizeOperandsFLAT(), llvm::SIInstrInfo::legalizeOperandsSMRD(), llvm::SIInstrInfo::legalizeOperandsVOP3(), llvm::SIInstrInfo::legalizeOpWithMove(), llvm::SIInstrInfo::loadRegFromStackSlot(), llvm::SIInstrInfo::materializeImmediate(), llvm::SITargetLowering::requiresUniformRegister(), llvm::SIInstrInfo::storeRegToStackSlot(), and llvm::SIInstrInfo::usesConstantBus().

◆ isSGPRClassID()

- Returns

- true if this class ID contains only SGPR registers

Definition at line 203 of file SIRegisterInfo.h.

References getRegClass(), and isSGPRClass().

◆ isSGPRReg()

| bool SIRegisterInfo::isSGPRReg | ( | const MachineRegisterInfo & | MRI, |

| Register | Reg | ||

| ) | const |

Definition at line 2866 of file SIRegisterInfo.cpp.

References isSGPRClass(), and MRI.

Referenced by llvm::SIInstrInfo::convertToThreeAddress(), llvm::SIInstrInfo::foldImmediate(), llvm::PhiLoweringHelper::isLaneMaskReg(), llvm::SIInstrInfo::isOperandLegal(), llvm::SIInstrInfo::isVGPRCopy(), llvm::SIInstrInfo::legalizeOperandsVOP2(), llvm::SIInstrInfo::mayReadEXEC(), llvm::SIInstrInfo::moveFlatAddrToVGPR(), and llvm::SIInstrInfo::verifyInstruction().

◆ isUniformReg()

|

override |

Definition at line 2970 of file SIRegisterInfo.cpp.

References llvm::RegisterBankInfo::getRegBank(), llvm::RegisterBankInfo::isDivergentRegBank(), and MRI.

◆ isVectorRegister()

|

inline |

◆ isVectorSuperClass()

|

inline |

- Returns

- true only if this class contains both VGPR and AGPR registers

Definition at line 220 of file SIRegisterInfo.h.

References hasAGPRs(), hasSGPRs(), and hasVGPRs().

Referenced by getProperlyAlignedRC(), and isProperlyAlignedRC().

◆ isVGPR()

| bool SIRegisterInfo::isVGPR | ( | const MachineRegisterInfo & | MRI, |

| Register | Reg | ||

| ) | const |

Definition at line 3008 of file SIRegisterInfo.cpp.

References getRegClassForReg(), isVGPRClass(), and MRI.

Referenced by llvm::SIInstrInfo::canShrink(), llvm::SIInstrInfo::foldImmediate(), isVectorRegister(), llvm::SIInstrInfo::legalizeOperandsVOP2(), llvm::SIInstrInfo::legalizeOperandsVOP3(), and llvm::SIInstrInfo::moveToVALUImpl().

◆ isVGPRClass()

|

inlinestatic |

- Returns

- true if this class contains only VGPR registers

Definition at line 210 of file SIRegisterInfo.h.

References hasAGPRs(), hasSGPRs(), and hasVGPRs().

Referenced by getLargestLegalSuperClass(), getProperlyAlignedRC(), llvm::SITargetLowering::getRegForInlineAsmConstraint(), getReservedRegs(), isProperlyAlignedRC(), and isVGPR().

◆ isVSSuperClass()

|

inline |

- Returns

- true only if this class contains both VGPR and SGPR registers

Definition at line 225 of file SIRegisterInfo.h.

References hasAGPRs(), hasSGPRs(), and hasVGPRs().

◆ materializeFrameBaseRegister()

|

override |

Definition at line 826 of file SIRegisterInfo.cpp.

References llvm::MachineInstrBuilder::addFrameIndex(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::MachineBasicBlock::begin(), llvm::BuildMI(), DL, llvm::GCNSubtarget::enableFlatScratch(), llvm::MachineBasicBlock::end(), llvm::GCNSubtarget::getInstrInfo(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getRegInfo(), llvm::RegState::Kill, MBB, MRI, llvm::Offset, and TII.

◆ needsFrameBaseReg()

|

override |

Definition at line 812 of file SIRegisterInfo.cpp.

References llvm::SIInstrFlags::FlatScratch, llvm::GCNSubtarget::getInstrInfo(), getScratchInstrOffset(), llvm::SIInstrInfo::isFLATScratch(), llvm::SIInstrInfo::isMUBUF(), MI, llvm::Offset, llvm::AMDGPUAS::PRIVATE_ADDRESS, and TII.

◆ opCanUseInlineConstant()

- Returns

- True if operands defined with this operand type can accept an inline constant. i.e. An integer value in the range (-16, 64) or -4.0f, -2.0f, -1.0f, -0.5f, 0.0f, 0.5f, 1.0f, 2.0f, 4.0f.

Definition at line 2912 of file SIRegisterInfo.cpp.

References llvm::GCNSubtarget::hasMFMAInlineLiteralBug(), llvm::AMDGPU::OPERAND_REG_INLINE_AC_FIRST, llvm::AMDGPU::OPERAND_REG_INLINE_AC_LAST, llvm::AMDGPU::OPERAND_SRC_FIRST, and llvm::AMDGPU::OPERAND_SRC_LAST.

Referenced by llvm::SIInstrInfo::isImmOperandLegal().

◆ opCanUseLiteralConstant()

- Returns

- True if operands defined with this operand type can accept a literal constant (i.e. any 32-bit immediate).

Definition at line 2945 of file SIRegisterInfo.cpp.

References llvm::AMDGPU::OPERAND_REG_IMM_FIRST, and llvm::AMDGPU::OPERAND_REG_IMM_LAST.

Referenced by llvm::SIInstrInfo::isImmOperandLegal().

◆ requiresFrameIndexReplacementScavenging()

|

override |

Definition at line 778 of file SIRegisterInfo.cpp.

References llvm::MachineFunction::getFrameInfo(), and llvm::MachineFrameInfo::hasStackObjects().

◆ requiresFrameIndexScavenging()

|

override |

Definition at line 769 of file SIRegisterInfo.cpp.

◆ requiresRegisterScavenging()

|

override |

Definition at line 758 of file SIRegisterInfo.cpp.

References llvm::MachineFunction::getFrameInfo(), llvm::MachineFunction::getInfo(), llvm::MachineFrameInfo::hasCalls(), llvm::MachineFrameInfo::hasStackObjects(), and Info.

◆ requiresVirtualBaseRegisters()

|

override |

Definition at line 784 of file SIRegisterInfo.cpp.

◆ reservedPrivateSegmentBufferReg()

| MCRegister SIRegisterInfo::reservedPrivateSegmentBufferReg | ( | const MachineFunction & | MF | ) | const |

Return the end register initially reserved for the scratch buffer in case spilling is needed.

Definition at line 559 of file SIRegisterInfo.cpp.

References getAlignedHighSGPRForRC().

◆ resolveFrameIndex()

|

override |

Definition at line 877 of file SIRegisterInfo.cpp.

References assert(), llvm::MachineOperand::ChangeToRegister(), llvm::SIInstrFlags::FlatScratch, llvm::MachineOperand::getImm(), llvm::GCNSubtarget::getInstrInfo(), llvm::MachineOperand::isFI(), llvm::MachineOperand::isImm(), llvm_unreachable, MI, llvm::Offset, llvm::AMDGPUAS::PRIVATE_ADDRESS, llvm::MachineOperand::setImm(), and TII.

◆ restoreSGPR()

| bool SIRegisterInfo::restoreSGPR | ( | MachineBasicBlock::iterator | MI, |

| int | FI, | ||

| RegScavenger * | RS, | ||

| SlotIndexes * | Indexes = nullptr, |

||

| LiveIntervals * | LIS = nullptr, |

||

| bool | OnlyToVGPR = false, |

||

| bool | SpillToPhysVGPRLane = false |

||

| ) | const |

Definition at line 1883 of file SIRegisterInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::SGPRSpillBuilder::DL, llvm::ArrayRef< T >::empty(), llvm::GCNSubtarget::getInstrInfo(), llvm::getKillRegState(), llvm::SGPRSpillBuilder::getPerVGPRData(), llvm::SIMachineFunctionInfo::getSGPRSpillToPhysicalVGPRLanes(), llvm::SIMachineFunctionInfo::getSGPRSpillToVirtualVGPRLanes(), llvm::RegState::ImplicitDefine, llvm::SlotIndexes::insertMachineInstrInMaps(), llvm::SGPRSpillBuilder::MBB, llvm::SGPRSpillBuilder::MFI, MI, llvm::SGPRSpillBuilder::NumSubRegs, llvm::Offset, llvm::SGPRSpillBuilder::prepare(), llvm::SGPRSpillBuilder::readWriteTmpVGPR(), llvm::LiveIntervals::removeAllRegUnitsForPhysReg(), llvm::SlotIndexes::replaceMachineInstrInMaps(), llvm::SGPRSpillBuilder::restore(), llvm::SGPRSpillBuilder::SplitParts, SubReg, llvm::SGPRSpillBuilder::SuperReg, llvm::SGPRSpillBuilder::TII, and llvm::SGPRSpillBuilder::TmpVGPR.

Referenced by eliminateFrameIndex(), and eliminateSGPRToVGPRSpillFrameIndex().

◆ shouldCoalesce()

|

override |

Definition at line 3023 of file SIRegisterInfo.cpp.

◆ shouldRealignStack()

|

override |

Definition at line 745 of file SIRegisterInfo.cpp.

References llvm::MachineFunction::getInfo(), Info, and llvm::TargetRegisterInfo::shouldRealignStack().

Referenced by hasBasePointer().

◆ shouldRewriteCopySrc()

|

override |

Definition at line 2921 of file SIRegisterInfo.cpp.

◆ spillEmergencySGPR()

| bool SIRegisterInfo::spillEmergencySGPR | ( | MachineBasicBlock::iterator | MI, |

| MachineBasicBlock & | RestoreMBB, | ||

| Register | SGPR, | ||

| RegScavenger * | RS | ||

| ) | const |

Definition at line 1963 of file SIRegisterInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::SIMachineFunctionInfo::addToSpilledSGPRs(), llvm::BuildMI(), llvm::SGPRSpillBuilder::DL, llvm::MachineBasicBlock::end(), llvm::GCNSubtarget::getInstrInfo(), llvm::getKillRegState(), llvm::SGPRSpillBuilder::getPerVGPRData(), llvm::RegState::Implicit, llvm::RegState::ImplicitDefine, llvm::SGPRSpillBuilder::IsKill, llvm::SGPRSpillBuilder::MBB, llvm::SGPRSpillBuilder::MFI, MI, llvm::SGPRSpillBuilder::NumSubRegs, llvm::Offset, llvm::SGPRSpillBuilder::prepare(), llvm::SGPRSpillBuilder::restore(), llvm::SGPRSpillBuilder::setMI(), llvm::SGPRSpillBuilder::SplitParts, SubReg, llvm::SGPRSpillBuilder::SuperReg, llvm::SGPRSpillBuilder::TII, llvm::SGPRSpillBuilder::TmpVGPR, and llvm::RegState::Undef.

◆ spillSGPR()

| bool SIRegisterInfo::spillSGPR | ( | MachineBasicBlock::iterator | MI, |

| int | FI, | ||

| RegScavenger * | RS, | ||

| SlotIndexes * | Indexes = nullptr, |

||

| LiveIntervals * | LIS = nullptr, |

||

| bool | OnlyToVGPR = false, |

||

| bool | SpillToPhysVGPRLane = false |

||

| ) | const |

If OnlyToVGPR is true, this will only succeed if this manages to find a free VGPR lane to spill.

Definition at line 1760 of file SIRegisterInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::SIMachineFunctionInfo::addToSpilledSGPRs(), assert(), llvm::BuildMI(), llvm::SGPRSpillBuilder::DL, llvm::ArrayRef< T >::empty(), llvm::SIMachineFunctionInfo::getFrameOffsetReg(), llvm::GCNSubtarget::getInstrInfo(), llvm::getKillRegState(), llvm::SGPRSpillBuilder::getPerVGPRData(), llvm::SIMachineFunctionInfo::getSGPRSpillToPhysicalVGPRLanes(), llvm::SIMachineFunctionInfo::getSGPRSpillToVirtualVGPRLanes(), llvm::SIMachineFunctionInfo::getStackPtrOffsetReg(), llvm::RegState::Implicit, llvm::RegState::ImplicitDefine, llvm::SlotIndexes::insertMachineInstrInMaps(), llvm::SGPRSpillBuilder::IsKill, llvm::SGPRSpillBuilder::MBB, llvm::SGPRSpillBuilder::MFI, MI, llvm::SGPRSpillBuilder::NumSubRegs, llvm::Offset, llvm::SGPRSpillBuilder::prepare(), llvm::SGPRSpillBuilder::readWriteTmpVGPR(), llvm::LiveIntervals::removeAllRegUnitsForPhysReg(), llvm::SlotIndexes::replaceMachineInstrInMaps(), llvm::SGPRSpillBuilder::restore(), llvm::ArrayRef< T >::size(), llvm::SGPRSpillBuilder::SplitParts, SubReg, llvm::SGPRSpillBuilder::SuperReg, llvm::SGPRSpillBuilder::TII, llvm::SGPRSpillBuilder::TmpVGPR, and llvm::RegState::Undef.

Referenced by eliminateFrameIndex(), and eliminateSGPRToVGPRSpillFrameIndex().

◆ spillSGPRToVGPR()

|

inline |

Definition at line 71 of file SIRegisterInfo.h.

Referenced by llvm::SIInstrInfo::loadRegFromStackSlot(), and llvm::SIInstrInfo::storeRegToStackSlot().

The documentation for this class was generated from the following files:

- lib/Target/AMDGPU/SIRegisterInfo.h

- lib/Target/AMDGPU/SIRegisterInfo.cpp