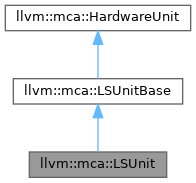

Default Load/Store Unit (LS Unit) for simulated processors. More...

#include "llvm/MCA/HardwareUnits/LSUnit.h"

Public Member Functions | |

| LSUnit (const MCSchedModel &SM) | |

| LSUnit (const MCSchedModel &SM, unsigned LQ, unsigned SQ) | |

| LSUnit (const MCSchedModel &SM, unsigned LQ, unsigned SQ, bool AssumeNoAlias) | |

| Status | isAvailable (const InstRef &IR) const override |

| Returns LSU_AVAILABLE if there are enough load/store queue entries to accomodate instruction IR. | |

| unsigned | dispatch (const InstRef &IR) override |

| Allocates LS resources for instruction IR. | |

| void | onInstructionExecuted (const InstRef &IR) override |

Public Member Functions inherited from llvm::mca::LSUnitBase Public Member Functions inherited from llvm::mca::LSUnitBase | |

| LSUnitBase (const MCSchedModel &SM, unsigned LoadQueueSize, unsigned StoreQueueSize, bool AssumeNoAlias) | |

| virtual | ~LSUnitBase () |

| unsigned | getLoadQueueSize () const |

| Returns the total number of entries in the load queue. | |

| unsigned | getStoreQueueSize () const |

| Returns the total number of entries in the store queue. | |

| unsigned | getUsedLQEntries () const |

| unsigned | getUsedSQEntries () const |

| void | acquireLQSlot () |

| void | acquireSQSlot () |

| void | releaseLQSlot () |

| void | releaseSQSlot () |

| bool | assumeNoAlias () const |

| virtual Status | isAvailable (const InstRef &IR) const =0 |

| This method checks the availability of the load/store buffers. | |

| virtual unsigned | dispatch (const InstRef &IR)=0 |

| Allocates LS resources for instruction IR. | |

| bool | isSQEmpty () const |

| bool | isLQEmpty () const |

| bool | isSQFull () const |

| bool | isLQFull () const |

| bool | isValidGroupID (unsigned Index) const |

| bool | isReady (const InstRef &IR) const |

| Check if a peviously dispatched instruction IR is now ready for execution. | |

| bool | isPending (const InstRef &IR) const |

| Check if instruction IR only depends on memory instructions that are currently executing. | |

| bool | isWaiting (const InstRef &IR) const |

| Check if instruction IR is still waiting on memory operations, and the wait time is still unknown. | |

| bool | hasDependentUsers (const InstRef &IR) const |

| const MemoryGroup & | getGroup (unsigned Index) const |

| MemoryGroup & | getGroup (unsigned Index) |

| unsigned | createMemoryGroup () |

| virtual void | onInstructionExecuted (const InstRef &IR) |

| virtual void | onInstructionRetired (const InstRef &IR) |

| virtual void | onInstructionIssued (const InstRef &IR) |

| virtual void | cycleEvent () |

| void | dump () const |

Public Member Functions inherited from llvm::mca::HardwareUnit Public Member Functions inherited from llvm::mca::HardwareUnit | |

| HardwareUnit ()=default | |

| virtual | ~HardwareUnit () |

Additional Inherited Members | |

Public Types inherited from llvm::mca::LSUnitBase Public Types inherited from llvm::mca::LSUnitBase | |

| enum | Status { LSU_AVAILABLE = 0 , LSU_LQUEUE_FULL , LSU_SQUEUE_FULL } |

Detailed Description

Default Load/Store Unit (LS Unit) for simulated processors.

Each load (or store) consumes one entry in the load (or store) queue.

Rules are: 1) A younger load is allowed to pass an older load only if there are no stores nor barriers in between the two loads. 2) An younger store is not allowed to pass an older store. 3) A younger store is not allowed to pass an older load. 4) A younger load is allowed to pass an older store only if the load does not alias with the store.

This class optimistically assumes that loads don't alias store operations. Under this assumption, younger loads are always allowed to pass older stores (this would only affects rule 4). Essentially, this class doesn't perform any sort alias analysis to identify aliasing loads and stores.

To enforce aliasing between loads and stores, flag AssumeNoAlias must be set to false by the constructor of LSUnit.

Note that this class doesn't know about the existence of different memory types for memory operations (example: write-through, write-combining, etc.). Derived classes are responsible for implementing that extra knowledge, and provide different sets of rules for loads and stores by overriding method isReady(). To emulate a write-combining memory type, rule 2. must be relaxed in a derived class to enable the reordering of non-aliasing store operations.

No assumptions are made by this class on the size of the store buffer. This class doesn't know how to identify cases where store-to-load forwarding may occur.

LSUnit doesn't attempt to predict whether a load or store hits or misses the L1 cache. To be more specific, LSUnit doesn't know anything about cache hierarchy and memory types. It only knows if an instruction "mayLoad" and/or "mayStore". For loads, the scheduling model provides an "optimistic" load-to-use latency (which usually matches the load-to-use latency for when there is a hit in the L1D). Derived classes may expand this knowledge.

Class MCInstrDesc in LLVM doesn't know about serializing operations, nor memory-barrier like instructions. LSUnit conservatively assumes that an instruction which mayLoad and has unmodeled side effects behave like a "soft" load-barrier. That means, it serializes loads without forcing a flush of the load queue. Similarly, instructions that both mayStore and have unmodeled side effects are treated like store barriers. A full memory barrier is a 'mayLoad' and 'mayStore' instruction with unmodeled side effects. This is obviously inaccurate, but this is the best that we can do at the moment.

Each load/store barrier consumes one entry in the load/store queue. A load/store barrier enforces ordering of loads/stores:

- A younger load cannot pass a load barrier.

- A younger store cannot pass a store barrier.

A younger load has to wait for the memory load barrier to execute. A load/store barrier is "executed" when it becomes the oldest entry in the load/store queue(s). That also means, all the older loads/stores have already been executed.

Constructor & Destructor Documentation

◆ LSUnit() [1/3]

|

inline |

◆ LSUnit() [2/3]

|

inline |

◆ LSUnit() [3/3]

|

inline |

Member Function Documentation

◆ dispatch()

Allocates LS resources for instruction IR.

This method assumes that a previous call to isAvailable(IR) succeeded returning LSU_AVAILABLE.

Rules are: By default, rules are:

- A store may not pass a previous store.

- A load may not pass a previous store unless flag 'NoAlias' is set.

- A load may pass a previous load.

- A store may not pass a previous load (regardless of flag 'NoAlias').

- A load has to wait until an older load barrier is fully executed.

- A store has to wait until an older store barrier is fully executed.

Implements llvm::mca::LSUnitBase.

Definition at line 69 of file LSUnit.cpp.

References llvm::mca::LSUnitBase::acquireLQSlot(), llvm::mca::LSUnitBase::acquireSQSlot(), llvm::mca::MemoryGroup::addInstruction(), llvm::mca::MemoryGroup::addSuccessor(), assert(), llvm::mca::LSUnitBase::assumeNoAlias(), llvm::mca::LSUnitBase::createMemoryGroup(), llvm::dbgs(), llvm::mca::LSUnitBase::getGroup(), llvm::mca::InstructionBase::getMayLoad(), llvm::mca::InstructionBase::getMayStore(), IR, llvm::mca::InstructionBase::isALoadBarrier(), llvm::mca::InstructionBase::isAStoreBarrier(), llvm::mca::MemoryGroup::isExecuting(), and LLVM_DEBUG.

Referenced by llvm::mca::InOrderIssueStage::execute().

◆ isAvailable()

|

overridevirtual |

Returns LSU_AVAILABLE if there are enough load/store queue entries to accomodate instruction IR.

Implements llvm::mca::LSUnitBase.

Definition at line 196 of file LSUnit.cpp.

References llvm::mca::InstructionBase::getMayLoad(), llvm::mca::InstructionBase::getMayStore(), IR, llvm::mca::LSUnitBase::isLQFull(), llvm::mca::LSUnitBase::isSQFull(), llvm::mca::LSUnitBase::LSU_AVAILABLE, llvm::mca::LSUnitBase::LSU_LQUEUE_FULL, and llvm::mca::LSUnitBase::LSU_SQUEUE_FULL.

◆ onInstructionExecuted()

Reimplemented from llvm::mca::LSUnitBase.

Definition at line 233 of file LSUnit.cpp.

References llvm::mca::Instruction::getLSUTokenID(), IR, llvm::mca::InstructionBase::isMemOp(), llvm::mca::LSUnitBase::isValidGroupID(), and llvm::mca::LSUnitBase::onInstructionExecuted().

The documentation for this class was generated from the following files:

- include/llvm/MCA/HardwareUnits/LSUnit.h

- lib/MCA/HardwareUnits/LSUnit.cpp