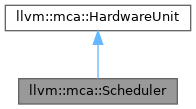

Class Scheduler is responsible for issuing instructions to pipeline resources. More...

#include "llvm/MCA/HardwareUnits/Scheduler.h"

Public Types | |

| enum | Status { SC_AVAILABLE , SC_LOAD_QUEUE_FULL , SC_STORE_QUEUE_FULL , SC_BUFFERS_FULL , SC_DISPATCH_GROUP_STALL } |

Public Member Functions | |

| Scheduler (const MCSchedModel &Model, LSUnitBase &Lsu) | |

| Scheduler (const MCSchedModel &Model, LSUnitBase &Lsu, std::unique_ptr< SchedulerStrategy > SelectStrategy) | |

| Scheduler (std::unique_ptr< ResourceManager > RM, LSUnitBase &Lsu, std::unique_ptr< SchedulerStrategy > SelectStrategy) | |

| Status | isAvailable (const InstRef &IR) |

| Check if the instruction in 'IR' can be dispatched during this cycle. | |

| bool | dispatch (InstRef &IR) |

| Reserves buffer and LSUnit queue resources that are necessary to issue this instruction. | |

| void | issueInstruction (InstRef &IR, SmallVectorImpl< std::pair< ResourceRef, ReleaseAtCycles > > &Used, SmallVectorImpl< InstRef > &Pending, SmallVectorImpl< InstRef > &Ready) |

| Issue an instruction and populates a vector of used pipeline resources, and a vector of instructions that transitioned to the ready state as a result of this event. | |

| bool | mustIssueImmediately (const InstRef &IR) const |

| Returns true if IR has to be issued immediately, or if IR is a zero latency instruction. | |

| void | cycleEvent (SmallVectorImpl< ResourceRef > &Freed, SmallVectorImpl< InstRef > &Executed, SmallVectorImpl< InstRef > &Pending, SmallVectorImpl< InstRef > &Ready) |

| This routine notifies the Scheduler that a new cycle just started. | |

| unsigned | getResourceID (uint64_t Mask) const |

| Convert a resource mask into a valid llvm processor resource identifier. | |

| InstRef | select () |

| Select the next instruction to issue from the ReadySet. | |

| bool | isReadySetEmpty () const |

| bool | isWaitSetEmpty () const |

| void | analyzeDataDependencies (SmallVectorImpl< InstRef > &RegDeps, SmallVectorImpl< InstRef > &MemDeps) |

| This method is called by the ExecuteStage at the end of each cycle to identify bottlenecks caused by data dependencies. | |

| uint64_t | analyzeResourcePressure (SmallVectorImpl< InstRef > &Insts) |

| Returns a mask of busy resources, and populates vector Insts with instructions that could not be issued to the underlying pipelines because not all pipeline resources were available. | |

| bool | hadTokenStall () const |

| void | dump () const |

| void | instructionCheck (const InstRef &IR) const |

Public Member Functions inherited from llvm::mca::HardwareUnit Public Member Functions inherited from llvm::mca::HardwareUnit | |

| HardwareUnit ()=default | |

| virtual | ~HardwareUnit () |

Detailed Description

Class Scheduler is responsible for issuing instructions to pipeline resources.

Internally, it delegates to a ResourceManager the management of processor resources. This class is also responsible for tracking the progress of instructions from the dispatch stage, until the write-back stage.

Definition at line 70 of file Scheduler.h.

Member Enumeration Documentation

◆ Status

| Enumerator | |

|---|---|

| SC_AVAILABLE | |

| SC_LOAD_QUEUE_FULL | |

| SC_STORE_QUEUE_FULL | |

| SC_BUFFERS_FULL | |

| SC_DISPATCH_GROUP_STALL | |

Definition at line 173 of file Scheduler.h.

Constructor & Destructor Documentation

◆ Scheduler() [1/3]

|

inline |

Definition at line 157 of file Scheduler.h.

◆ Scheduler() [2/3]

|

inline |

Definition at line 160 of file Scheduler.h.

◆ Scheduler() [3/3]

|

inline |

Definition at line 165 of file Scheduler.h.

Member Function Documentation

◆ analyzeDataDependencies()

| void llvm::mca::Scheduler::analyzeDataDependencies | ( | SmallVectorImpl< InstRef > & | RegDeps, |

| SmallVectorImpl< InstRef > & | MemDeps | ||

| ) |

This method is called by the ExecuteStage at the end of each cycle to identify bottlenecks caused by data dependencies.

Vector RegDeps is populated by instructions that were not issued because of unsolved register dependencies. Vector MemDeps is populated by instructions that were not issued because of unsolved memory dependencies.

Definition at line 248 of file Scheduler.cpp.

References llvm::SmallVectorImpl< T >::emplace_back(), llvm::mca::InstructionBase::getDesc(), IR, llvm::mca::InstructionBase::isMemOp(), llvm::mca::Instruction::isPending(), llvm::mca::LSUnitBase::isPending(), and llvm::make_range().

Referenced by llvm::mca::ExecuteStage::cycleEnd().

◆ analyzeResourcePressure()

| uint64_t llvm::mca::Scheduler::analyzeResourcePressure | ( | SmallVectorImpl< InstRef > & | Insts | ) |

Returns a mask of busy resources, and populates vector Insts with instructions that could not be issued to the underlying pipelines because not all pipeline resources were available.

Definition at line 243 of file Scheduler.cpp.

References llvm::append_range().

Referenced by llvm::mca::ExecuteStage::cycleEnd().

◆ cycleEvent()

| void llvm::mca::Scheduler::cycleEvent | ( | SmallVectorImpl< ResourceRef > & | Freed, |

| SmallVectorImpl< InstRef > & | Executed, | ||

| SmallVectorImpl< InstRef > & | Pending, | ||

| SmallVectorImpl< InstRef > & | Ready | ||

| ) |

This routine notifies the Scheduler that a new cycle just started.

It notifies the underlying ResourceManager that a new cycle just started. Vector Freed is populated with resourceRef related to resources that have changed in state, and that are now available to new instructions. Instructions executed are added to vector Executed, while vector Ready is populated with instructions that have become ready in this new cycle. Vector Pending is popluated by instructions that have transitioned through the pending stat during this cycle. The Pending and Ready sets may not be disjoint. An instruction is allowed to transition from the WAIT state to the READY state (going through the PENDING state) within a single cycle. That means, instructions may appear in both the Pending and Ready set.

Definition at line 264 of file Scheduler.cpp.

References llvm::mca::LSUnitBase::cycleEvent(), and IR.

Referenced by llvm::mca::ExecuteStage::cycleStart().

◆ dispatch()

Reserves buffer and LSUnit queue resources that are necessary to issue this instruction.

Returns true if instruction IR is ready to be issued to the underlying pipelines. Note that this operation cannot fail; it assumes that a previous call to method isAvailable(IR) returned SC_AVAILABLE.

If IR is a memory operation, then the Scheduler queries the LS unit to obtain a LS token. An LS token is used internally to track memory dependencies.

Definition at line 300 of file Scheduler.cpp.

References assert(), llvm::dbgs(), llvm::mca::LSUnitBase::dispatch(), llvm::mca::Instruction::getUsedBuffers(), IR, llvm::mca::Instruction::isDispatched(), llvm::mca::InstructionBase::isMemOp(), llvm::mca::Instruction::isPending(), llvm::mca::LSUnitBase::isPending(), llvm::mca::Instruction::isReady(), llvm::mca::LSUnitBase::isReady(), llvm::mca::LSUnitBase::isWaiting(), LLVM_DEBUG, mustIssueImmediately(), and llvm::mca::Instruction::setLSUTokenID().

Referenced by llvm::mca::ExecuteStage::execute().

◆ dump()

| void llvm::mca::Scheduler::dump | ( | ) | const |

Definition at line 32 of file Scheduler.cpp.

References llvm::dbgs().

◆ getResourceID()

Convert a resource mask into a valid llvm processor resource identifier.

Only the most significant bit of the Mask is used by this method to identify the processor resource.

Definition at line 234 of file Scheduler.h.

Referenced by llvm::mca::ExecuteStage::notifyInstructionIssued(), and llvm::mca::ExecuteStage::notifyReservedOrReleasedBuffers().

◆ hadTokenStall()

|

inline |

Definition at line 261 of file Scheduler.h.

Referenced by llvm::mca::ExecuteStage::cycleEnd().

◆ instructionCheck()

Definition at line 270 of file Scheduler.h.

References assert(), IR, and llvm::is_contained().

Referenced by llvm::mca::ExecuteStage::execute().

◆ isAvailable()

| Scheduler::Status llvm::mca::Scheduler::isAvailable | ( | const InstRef & | IR | ) |

Check if the instruction in 'IR' can be dispatched during this cycle.

Return SC_AVAILABLE if both scheduler and LS resources are available.

This method is also responsible for setting field HadTokenStall if IR cannot be dispatched to the Scheduler due to unavailable resources.

Definition at line 40 of file Scheduler.cpp.

References IR, llvm::mca::LSUnitBase::isAvailable(), llvm_unreachable, llvm::mca::LSUnitBase::LSU_AVAILABLE, llvm::mca::LSUnitBase::LSU_LQUEUE_FULL, llvm::mca::LSUnitBase::LSU_SQUEUE_FULL, llvm::mca::RS_BUFFER_AVAILABLE, llvm::mca::RS_BUFFER_UNAVAILABLE, llvm::mca::RS_RESERVED, SC_AVAILABLE, SC_BUFFERS_FULL, SC_DISPATCH_GROUP_STALL, SC_LOAD_QUEUE_FULL, and SC_STORE_QUEUE_FULL.

Referenced by llvm::mca::ExecuteStage::isAvailable().

◆ isReadySetEmpty()

|

inline |

Definition at line 243 of file Scheduler.h.

◆ issueInstruction()

| void llvm::mca::Scheduler::issueInstruction | ( | InstRef & | IR, |

| SmallVectorImpl< std::pair< ResourceRef, ReleaseAtCycles > > & | Used, | ||

| SmallVectorImpl< InstRef > & | Pending, | ||

| SmallVectorImpl< InstRef > & | Ready | ||

| ) |

Issue an instruction and populates a vector of used pipeline resources, and a vector of instructions that transitioned to the ready state as a result of this event.

Definition at line 99 of file Scheduler.cpp.

References llvm::mca::Instruction::getUsedBuffers(), llvm::mca::InstructionBase::hasDependentUsers(), llvm::mca::LSUnitBase::hasDependentUsers(), IR, and llvm::mca::InstructionBase::isMemOp().

◆ isWaitSetEmpty()

|

inline |

Definition at line 244 of file Scheduler.h.

◆ mustIssueImmediately()

Returns true if IR has to be issued immediately, or if IR is a zero latency instruction.

Definition at line 290 of file Scheduler.cpp.

References IR.

Referenced by dispatch(), and llvm::mca::ExecuteStage::execute().

◆ select()

| InstRef llvm::mca::Scheduler::select | ( | ) |

Select the next instruction to issue from the ReadySet.

Returns an invalid instruction reference if there are no ready instructions, or if processor resources are not available.

Definition at line 192 of file Scheduler.cpp.

References E, llvm::mca::InstructionBase::getDesc(), I, IR, llvm::mca::Instruction::setCriticalResourceMask(), and std::swap().

The documentation for this class was generated from the following files:

- include/llvm/MCA/HardwareUnits/Scheduler.h

- lib/MCA/HardwareUnits/Scheduler.cpp