## arm

Function Multi Versioning for AArch64: Compiler aided function specialization with runtime dispatch

**Alexandros Lamprineas**

### Intro

### The problem

- Software is deployed on various devices (we may compile for a baseline and reuse the binaries).

- Most CPUs implement optional instructions which may not be present on the target of compilation.

- For example, on Arm, dotproduct instructions may not be available.

- To make use of such instructions, a run-time check is needed.

#### The solution

Function Multi Versioning (FMV)

https://learn.arm.com/learning-paths/cross-platform/function-multiversioning

- lets the compiler generate multiple function versions, and

- auto-dispatch between them

### What's new?

- FMV was originally developed for x86 using the function attributes target and target\_clones

- attribute ((target("sse4.2"))) https://llvm.org/devmtg/2014-10/#talk22

- https://reviews.llvm.org/D40819

- On AArch64 the target attribute is broadly used as an optimization hint,

- for example in header files of Arm C Language Extensions:

#### lib/clang/21/include/arm\_acle.h

```

#if defined( ARM 64BIT STATE) && ARM 64BIT STATE

uint64_t val[8];

data512 t:

static __inline__ data512_t __attribute__((__always_inline__, __nodebug__, target("ls64")))

arm ld64b(const void * addr) {

data512 t value:

builtin_arm_ld64b( addr, value.val);

value:

```

Therefore, we introduced a new attribute target\_version (also adopted by RISC-V) and wrote a specification for FMV in ACLE (currently beta).

### Clang CodeGen

- Clang generates multiple function versions with mangled names as per https://arm-software.github.io/acle/main/acle.html#name-mangling

- each version may use several features, their names are encoded in the mangled name

- \_\_attribute((target\_version("crc+bti+aes+bf16"))) int fmv(void); → @fmv.\_MaesMbf16MbtiMcrc()

- Each version is associated with metadata which propagate information from C/C++ source to LLVM.

- Clang generates a resolver function that determines which version to run when the function is called.

- The resolution is dynamic (it is performed at load time) and permanent for the lifetime of the process.

- The resolver: (1) initializes the runtime, (2) detects features, and (3) selects the available version of highest priority as indicated by <a href="https://arm-software.github.io/acle/main/acle.html#mapping">https://arm-software.github.io/acle/main/acle.html#mapping</a>

- Clang generates a global \_\_aarch64\_cpu\_features which contains the feature bits for runtime detection.

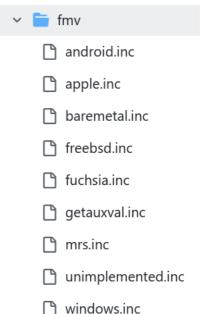

### Compiler-rt

The runtime asks the kernel which features are available on host and initializes <u>\_\_aarch64\_cpu\_features</u>

Ilvm-project / compiler-rt / lib / builtins / cpu model / aarch64 / fmv / mrs.inc #if \_\_has\_include(<sys/auxv.h>) #include <sys/auxv.h> #define HAVE SYS AUXV H 3 #endif 5 static void \_\_init\_cpu\_features\_constructor(unsigned long hwcap, const \_\_ifunc\_arg\_t \*arg) { unsigned long long feat = 0; 8 #define setCPUFeature(F) feat |= 1ULL << F</pre> #define getCPUFeature(id, ftr) \_\_asm\_\_("mrs %0, " #id : "=r"(ftr)) 10 #define extractBits(val, start, number) 11 (val & ((1ULL << number) - 1ULL) << start) >> start 12 unsigned long hwcap2 = 0; 13 14 if (hwcap & \_IFUNC\_ARG\_HWCAP) 15 hwcap2 = arg -> hwcap2;if (hwcap & HWCAP\_CRC32) 16 setCPUFeature(FEAT\_CRC); 17 if (hwcap & HWCAP\_SHA3) 103 setCPUFeature(FEAT\_SHA3); 104 setCPUFeature(FEAT\_INIT); 105 106 atomic store n(& aarch64 cpu features.features, feat, ATOMIC RELAXED); 107 108

#### Various platforms are supported

### Example

#### https://godbolt.org/z/qsaTohfM7

```

E COMPILER EXPLORER

armv8-a clang (trunk) (Editor #1) 0 X

Add... ▼ More ▼ Templates 🚯

--target=aarch64-linux-gnu -march=armv8-a -O3 --rtlib=compiler-rt -S -emit-llvm

armv8-a clang (trunk)

C source #1 0

@__aarch64_cpu_features = external dso_local global { i64 }

⊚ C

A - Save/Load + Add new... - V Vim

#include <stdio.h>

@CopyWord = weak_odr dso_local ifunc ptr (ptr, ptr), ptr @CopyWord.resolver

#include <string.h>

@SkipWord = weak_odr dso_local ifunc ptr (ptr, ptr), ptr @SkipWord.resolver

3

__attribute__((target_clones("default", "mops")))

define dso local ptr @CopyWord. Mmops(ptr noundef %0, ptr noundef %1) #0 {

char *CopyWord(char *dst, const char *src) {

define dso local ptr @CopyWord.default(ptr noundef %0, ptr noundef %1) #5 {

172

6

size_t n = strlen(src);

memcpy(dst, src, n + 1);

define dso_local ptr @SkipWord._Msve2(ptr noundef %0, ptr noundef %1) #3 {

8

return dst + n;

52

9

define dso_local ptr @SkipWord.default(ptr noundef %0, ptr noundef %1) #5 {

10

__attribute__((target_version("sve2")))

attributes #0 = { noinline nounwind optnone uwtable "fmv-features"="mops"

const char *SkipWord(const char *p, const char *end) {

"target-features"="+fp-armv8, +mops, +neon, +outline-atomics, +v8a" }

13

printf("Running the sve2 SkipWord\n");

__asm volatile (

14

attributes #3 = { noinline nounwind optnone uwtable "fmv-features"="sve2"

15

"mov w2, #0xd090000\n\t"

"target-features"="+fp-armv8, +fullfp16, +neon, +outline-atomics, +sve, +sve2, +v8a" }

16

"add w2, w2, #0xa20\n\t"

17

"mov z1.s, w2\n\t"

attributes #5 = { noinline nounwind optnone uwtable "fmv-features"

18

"whilelt p0.b, %0, %1\n"

"target-features"="+fp-armv8, +neon, +outline-atomics, +v8a" }

19

"1:\n\t"

20

"ld1b z0.b, p0/z, [%0]\n\t"

__attribute__((target_version("default")))

declare dso_local void @__init_cpu_features_resolver()

21

"match p1.b, p0/z, z0.b, z1.b\n\t"

const char *SkipWord(const char *p, const char *end) {

22

"b.anv 2f\n\t"

40

printf("Running the default SkipWord\n");

"incb %0\n\t"

23

while (p != end && *p != ' ' && *p != '\n' && *p != '\r' && *p != '\t')

41

24

"whilelt p0.b, %0, %1\n\t"

42

p++;

25

"b.first 1b\n\t"

43

return p;

define weak_odr ptr @SkipWord.resolver() comdat {

111

26

"mov %0, %1\n\t"

44

tail call void @__init_cpu_features_resolver()

112

"b 3f\n"

27

45

113

%1 = load i64, ptr @__aarch64_cpu_features, align 8

28

"2:\n\t"

int main(int argc, char **argv) {

29

"brkb p2.b, p0/z, p1.b\n\t"

114

%2 = and 164 %1, 69793284352

if (argc != 3)

"incp %0, p2.b\n"

30

115

%3 = icmp eq 164 %2, 69793284352

return -1;

48

31

"3:\n\t"

%4 = select i1 %3, ptr @SkipWord._Msve2, ptr @SkipWord.default

49

char buffer[256];

116

32

: "+r" (p)

char *end = CopyWord(buffer, argv[1]);

50

117

ret ptr %4

33

: "r" (end)

end = CopyWord(end, argv[2]);

118

34

: "w2", "p0", "p1", "p2", "z0", "z1")

printf("%s\n", buffer);

35

return p;

printf("%s\n", SkipWord(buffer, buffer + strlen(buffer)));

36

54

return 0;

arm

55

Public © 2025 Arm 6

```

## Design choices

#### Resolver emission

- FMV is supported across multiple translation units.

- The resolver cannot "see" versions beyond the current translation unit.

- Emission options:

- On use (when the function is called)? → may generate multiple (potentially different) resolvers

→ non deterministic version selection depending on linking order \*\*

- Unique resolver in the TU of the default version

- → deterministic version selection regardless of linking order

#### Feature detection

- Dependent-on features get detected transitively as indicated by

https://arm-software.github.io/acle/main/acle.html#dependencies

(for example sve2→ sve → fp16 → fp)

- Features implied by the command line are not exempt from runtime detection (simd  $\rightarrow$  fp)

- For example -march=armv8 implies simd

### FMV info representation

FMV info is autogenerated using <a href="mailto:llvm/utils/TableGen/ArmTargetDefEmitter.cpp">llvm/utils/TableGen/ArmTargetDefEmitter.cpp</a> <a href="https://github.com/llvm/llvm-project/pull/113281">https://github.com/llvm/llvm-project/pull/113281</a>

```

Ilvm-project / Ilvm / include / Ilvm / TargetParser / AArch64TargetParser.h 📮

```

features for code generation

#### Ilvm-project / Ilvm / include / Ilvm / TargetParser / AArch64FeatPriorities.inc

```

// Represents a dependency between two architecture extensions. Later is the

84

// feature which was added to the architecture after Earlier, and expands the

85

// functionality provided by it. If Later is enabled, then Earlier will also be

86

// enabled. If Earlier is disabled, then Later will also be disabled.

87

struct ExtensionDependency {

88

ArchExtKind Earlier;

89

dependencies

ArchExtKind Later;

90

are used both for (1) runtime detection, and

};

91

(2) to enable all the necessary subtarget

```

```

// Function Multi Versioning feature priorities.

// enum FeatPriorities {

PRIOR_RNG,

PRIOR_FLAGM,

PRIOR_FLAGM2,

PRIOR_LSE,

PRIOR_FP,

```

```

// Function Multi Versioning CPU features.

24 ∨ enum CPUFeatures {

FEAT_RNG,

25

FEAT_FLAGM,

26

27

FEAT_FLAGM2,

detection ≠ priority

FEAT_FP16FML,

28

because the detection bit is

FEAT DOTPROD,

29

part of the ABI; if a feature is

30

FEAT_SM4,

FEAT_RDM,

31

added/removed whose priority

32

FEAT LSE,

falls between existing ones...

33

FEAT_FP,

FEAT_SIMD,

34

FEAT_CRC,

35

RESERVED FEAT SHA1, // previously used and now ABI legacy

36

37

FEAT_SHA2,

```

### Metadata in LLVM IR

• <a href="https://github.com/llvm/llvm-project/pull/118544">https://github.com/llvm/llvm-project/pull/118544</a>

Similar to target-features.

#### clang/test/CodeGen/AArch64/fmv-features.c

```

+ // CHECK: define dso_local i32 @fmv._MaesMbf16MbtiMcrc() #[[unordered_features_with_duplicates:[0-9]+]] {

+ __attribute__((target_version("crc+bti+bti+aes+aes+bf16"))) int fmv(void) { return 0; }

+ // CHECK: attributes #[[unordered_features_with_duplicates]] = {{\darksymbol{.*}}} "fmv-features"="aes,bf16,bti,crc"

```

#### Why we need them?

- Suppose you have target\_version("i8mm+dotprod") and target\_version("fcma").

- The first version has higher priority because Priority(i8mm) > Priority(fcma) > Priority(dotprod).

- Now suppose you specify -march=armv8-a+i8mm on the command line.

- Then the versions would have target-features "+dotprod,+i8mm" and "+fcma,+i8mm" respectively.

- If you are using these metadata to deduce version priority, then you would incorrectly deduce that the second version was higher priority than the first!

## **GlobalOpt**

May statically (at compile time) resolve calls to versioned functions <a href="https://github.com/llvm/llvm-project/pull/87939">https://github.com/llvm/llvm-project/pull/87939</a>

benefit? → inlining

by comparing LLVM IR metadata between caller and callee.

```

+ uint64_t AArch64TTIImpl::getFeatureMask(const Function &F) const {

StringRef AttributeStr =

253

isMultiversionedFunction(F) ? "fmv-features" : "target-features";

254

StringRef FeatureStr = F.getFnAttribute(AttributeStr).getValueAsString();

255

SmallVector<StringRef, 8> Features;

256

metadata selection

FeatureStr.split(Features, ",");

return AArch64::getFMVPriority(Features);

258

259

+ }

260

+ bool AArch64TTIImpl::isMultiversionedFunction(const Function &F) const {

return F.hasFnAttribute("fmv-features");

263

+ }

264 +

```

- if FMV caller → FMV callee, then compare fmv-features

- else if non-FMV caller → FMV callee,

then compare target-features with fmv-features

```

uint64_t AArch64::getFMVPriority(ArrayRef<StringRef> Features) {

// Transitively enable the Arch Extensions which correspond to each feature.

60

ExtensionSet FeatureBits;

for (const StringRef Feature : Features) {

std::optional<FMVInfo> FMV = parseFMVExtension(Feature);

62

if (!FMV) {

63

if (std::optional<ExtensionInfo> Info = targetFeatureToExtension(Feature))

64

FMV = lookupFMVByID(Info->ID);

65

bitmask construction

66

if (FMV && FMV->ID)

67

FeatureBits.enable(*FMV->ID);

68

69

70

// Construct a bitmask for all the transitively enabled Arch Extensions.

71

uint64_t PriorityMask = 0;

for (const FMVInfo &Info : getFMVInfo())

73

if (Info.ID && FeatureBits.Enabled.test(*Info.ID))

74

PriorityMask |= (1ULL << Info.PriorityBit);</pre>

75

76

return PriorityMask;

78

```

## Static resolution algorithm

```

+ // Follows the use-def chain of \p V backwards until it finds a Function,

+ // in which case it collects in \p Versions. Return true on successful

2645

+ // use-def chain traversal, false otherwise.

2646

+ static bool collectVersions(TargetTransformInfo &TTI, Value *V,

2647

2648

SmallVectorImpl<Function *> &Versions) {

if (auto *F = dyn_cast<Function>(V)) {

2649

discover callee

if (!TTI.isMultiversionedFunction(*F))

2650

versions

2651

return false;

Versions.push_back(F);

2652

} else if (auto *Sel = dyn_cast<SelectInst>(V)) {

2653

2654

if (!collectVersions(TTI, Sel->getTrueValue(), Versions))

return false;

2655

if (!collectVersions(TTI, Sel->getFalseValue(), Versions))

2656

2657

return false;

} else if (auto *Phi = dyn_cast<PHINode>(V)) {

2658

for (unsigned I = 0, E = Phi->getNumIncomingValues(); I != E; ++I)

2659

if (!collectVersions(TTI, Phi->getIncomingValue(I), Versions))

2660

2661

return false;

} else {

2662

// Unknown instruction type. Bail.

2663

2664

return false;

2665

```

```

labrinea marked this conversation as resolved.

```

• Show resolved

```

+ return true;

2667 + }

```

```

+ static bool OptimizeNonTrivialIFuncs(

2686

Module &M, function_ref<TargetTransformInfo &(Function &)> GetTTI) {

2687

bool Changed = false;

2688

2689

// Cache containing the mask constructed from a function's target features.

2690

for every ifunc in

DenseMap<Function *, uint64_t> FeatureMask;

2691

2692

the module

for (GlobalIFunc &IF : M.ifuncs()) {

2693

// Discover the callee versions.

2706

2707

SmallVector<Function *> Callees;

2708

if (any_of(*Resolver, [&TTI, &Callees](BasicBlock &BB) {

2709

if (auto *Ret = dyn_cast_or_null<ReturnInst>(BB.getTerminator()))

2710

if (!collectVersions(TTI, Ret->getReturnValue(), Callees))

2711

return true;

examine basic blocks

2712

return false;

2713

}))

of resolver

2714 +

continue;

2715

assert(!Callees.empty() && "Expecting successful collection of versions");

2716

2725

// Sort the callee versions in decreasing priority order.

sort(Callees, [&](auto *LHS, auto *RHS) {

sorts callees

2726

return FeatureMask[LHS] > FeatureMask[RHS];

2727 +

2730

// Find the callsites and cache the feature mask for each caller.

2731

SmallVector<Function *> Callers;

2732

DenseMap<Function *, SmallVector<CallBase *>> CallSites;

2733

for (User *U : IF.users()) {

discover

2734 +

if (auto *CB = dyn_cast<CallBase>(U)) {

caller versions

2735 +

if (CB->getCalledOperand() == &IF) {

2736

Function *Caller = CB->getFunction();

2748

// Sort the caller versions in decreasing priority order

sorts callers

sort(Callers, [&](auto *LHS, auto *RHS) {

2749

return FeatureMask[LHS] > FeatureMask[RHS];

2750 +

```

## Static resolution algorithm (continued)

```

auto implies = [](uint64_t A, uint64_t B) { return (A & B) == B; };

2753 +

2754

// Index to the highest priority candidate.

2755

unsigned I = 0;

2756

// Now try to redirect calls starting from higher priority callers.

2757

for (Function *Caller : Callers) {

2758

assert(I < Callees.size() && "Found callers of equal priority");</pre>

2759

2760

Function *Callee = Callees[I];

2761

uint64_t CallerBits = FeatureMask[Caller];

2762

uint64_t CalleeBits = FeatureMask[Callee];

2763

2764

// In the case of FMV callers, we know that all higher priority callers

2765

// than the current one did not get selected at runtime, which helps

2766

// reason about the callees (if they have versions that mandate presence

2767

// of the features which we already know are unavailable on this target).

2768

2769

if (TTI.isMultiversionedFunction(*Caller)) {

// If the feature set of the caller implies the feature set of the

2770

// highest priority candidate then it shall be picked. In case of

2771

2772

// identical sets advance the candidate index one position.

2773

if (CallerBits == CalleeBits)

2774

++I;

```

#### sorted caller versions

$\rightarrow$  caller.\_MmopsMsve2 = {1,1,1,1,1}  $\rightarrow$  callee.\_Mmops = {1,0,0,0,0} caller.  $Mmops = \{1,0,0,0,0\}$ callee. Msve2 =  $\{0,1,1,1,1\}$ caller.\_Msve =  $\{0,0,1,1,1\}$ callee.\_Msve =  $\{0,0,1,1,1\}$ → callee.default = {0,0,0,0,0} caller.default =  $\{0,0,0,0,0,0\}$  -

#### arm

#### Example <a href="https://godbolt.org/z/PcGnGbWd3">https://godbolt.org/z/PcGnGbWd3</a> from Ilvm/test/Transforms/GlobalOpt/resolve-fmv-ifunc.Il

2776

2777

2778

2779

2780

2781

2782

2783

2784

2785

2786

2787

2788

2789

2790

2791

2792

2793

2794

2795

sorted callee versions

```

2775 +

else if (!implies(CallerBits, CalleeBits)) {

// Keep advancing the candidate index as long as the caller's

// features are a subset of the current candidate's.

while (implies(CalleeBits, CallerBits)) {

if (++I == Callees.size())

break;

CalleeBits = FeatureMask[Callees[I]];

continue;

} else {

// We can't reason much about non-FMV callers. Just pick the highest

// priority callee if it matches, otherwise bail.

if (I > 0 || !implies(CallerBits, CalleeBits))

continue;

Simplified priority bitmask

after dependency expansion:

auto &Calls = CallSites[Caller];

for (CallBase *CS : Calls)

CS->setCalledOperand(Callee);

{mops,sve2,sve,fp16,fp}

Changed = true;

```

- mops+sve2 implies mops  $\rightarrow$  we can statically resolve

- mops implies mops  $\rightarrow$  we can statically resolve bitmask equality → advance callee iterator

- at this point we know the host does not have mops sve does not imply sve2  $\rightarrow$  we can't statically resolve however sve2 implies sve  $\rightarrow$  advance callee iterator

- keep skipping over callee candidates sve implies sve  $\rightarrow$  advance callee iterator

- no feature is available → we can statically resolve

### Future work

- User can control feature priorities: <a href="https://github.com/ARM-software/acle/pull/371">https://github.com/ARM-software/acle/pull/371</a>

- User can refer to a specific function version: <a href="https://github.com/llvm/llvm-project/issues/84094">https://github.com/llvm/llvm-project/issues/84094</a>

- Pointer authentication works with IFUNC resolver: <a href="https://github.com/llvm/llvm-project/pull/84704">https://github.com/llvm/llvm-project/pull/84704</a>

- Request to support more features (like CSSC): <a href="https://github.com/llvm/llvm-project/issues/131218">https://github.com/llvm/llvm-project/issues/131218</a>

- ? (feedback welcome)

## Acknowledgements

Special thanks to all the folks who helped with ACLE/code reviews, code refactoring, technical discussions, brainstorming, presentation, etc.

Jon Roelofs, Tomas Matheson, Andrew Carlotti, Daniel Kiss, Wilco Dijkstra, Victor Campos, Sander De Smalen, Maciej Gabka, Andre Vieira, Richard Sandiford, Pavel Iliin, Kristof Beyls, Alfie Richards and others.

# arm

Merci Danke Gracias Grazie 谢谢 ありがとう **Asante** Thank You 감사합니다 धन्यवाद Kiitos شکرًا ধন্যবাদ תודה ధన్యవాదములు Köszönöm

# arm

The Arm trademarks featured in this presentation are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. All other marks featured may be trademarks of their respective owners.