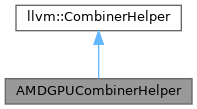

#include "Target/AMDGPU/AMDGPUCombinerHelper.h"

Public Member Functions | |

| bool | matchFoldableFneg (MachineInstr &MI, MachineInstr *&MatchInfo) |

| void | applyFoldableFneg (MachineInstr &MI, MachineInstr *&MatchInfo) |

| bool | matchExpandPromotedF16FMed3 (MachineInstr &MI, Register Src0, Register Src1, Register Src2) |

| void | applyExpandPromotedF16FMed3 (MachineInstr &MI, Register Src0, Register Src1, Register Src2) |

Public Member Functions inherited from llvm::CombinerHelper Public Member Functions inherited from llvm::CombinerHelper | |

| CombinerHelper (GISelChangeObserver &Observer, MachineIRBuilder &B, bool IsPreLegalize, GISelKnownBits *KB=nullptr, MachineDominatorTree *MDT=nullptr, const LegalizerInfo *LI=nullptr) | |

| GISelKnownBits * | getKnownBits () const |

| MachineIRBuilder & | getBuilder () const |

| const TargetLowering & | getTargetLowering () const |

| bool | isPreLegalize () const |

| bool | isLegal (const LegalityQuery &Query) const |

| bool | isLegalOrBeforeLegalizer (const LegalityQuery &Query) const |

| bool | isConstantLegalOrBeforeLegalizer (const LLT Ty) const |

| void | replaceRegWith (MachineRegisterInfo &MRI, Register FromReg, Register ToReg) const |

| MachineRegisterInfo::replaceRegWith() and inform the observer of the changes. | |

| void | replaceRegOpWith (MachineRegisterInfo &MRI, MachineOperand &FromRegOp, Register ToReg) const |

| Replace a single register operand with a new register and inform the observer of the changes. | |

| void | replaceOpcodeWith (MachineInstr &FromMI, unsigned ToOpcode) const |

| Replace the opcode in instruction with a new opcode and inform the observer of the changes. | |

| const RegisterBank * | getRegBank (Register Reg) const |

Get the register bank of Reg. | |

| void | setRegBank (Register Reg, const RegisterBank *RegBank) |

Set the register bank of Reg. | |

| bool | tryCombineCopy (MachineInstr &MI) |

If MI is COPY, try to combine it. | |

| bool | matchCombineCopy (MachineInstr &MI) |

| void | applyCombineCopy (MachineInstr &MI) |

| bool | isPredecessor (const MachineInstr &DefMI, const MachineInstr &UseMI) |

Returns true if DefMI precedes UseMI or they are the same instruction. | |

| bool | dominates (const MachineInstr &DefMI, const MachineInstr &UseMI) |

Returns true if DefMI dominates UseMI. | |

| bool | tryCombineExtendingLoads (MachineInstr &MI) |

If MI is extend that consumes the result of a load, try to combine it. | |

| bool | matchCombineExtendingLoads (MachineInstr &MI, PreferredTuple &MatchInfo) |

| void | applyCombineExtendingLoads (MachineInstr &MI, PreferredTuple &MatchInfo) |

| bool | matchCombineLoadWithAndMask (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Match (and (load x), mask) -> zextload x. | |

| bool | matchCombineExtractedVectorLoad (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Combine a G_EXTRACT_VECTOR_ELT of a load into a narrowed load. | |

| bool | matchCombineIndexedLoadStore (MachineInstr &MI, IndexedLoadStoreMatchInfo &MatchInfo) |

| void | applyCombineIndexedLoadStore (MachineInstr &MI, IndexedLoadStoreMatchInfo &MatchInfo) |

| bool | matchSextTruncSextLoad (MachineInstr &MI) |

| void | applySextTruncSextLoad (MachineInstr &MI) |

| bool | matchSextInRegOfLoad (MachineInstr &MI, std::tuple< Register, unsigned > &MatchInfo) |

| Match sext_inreg(load p), imm -> sextload p. | |

| void | applySextInRegOfLoad (MachineInstr &MI, std::tuple< Register, unsigned > &MatchInfo) |

| bool | matchCombineDivRem (MachineInstr &MI, MachineInstr *&OtherMI) |

| Try to combine G_[SU]DIV and G_[SU]REM into a single G_[SU]DIVREM when their source operands are identical. | |

| void | applyCombineDivRem (MachineInstr &MI, MachineInstr *&OtherMI) |

| bool | matchOptBrCondByInvertingCond (MachineInstr &MI, MachineInstr *&BrCond) |

| If a brcond's true block is not the fallthrough, make it so by inverting the condition and swapping operands. | |

| void | applyOptBrCondByInvertingCond (MachineInstr &MI, MachineInstr *&BrCond) |

| bool | matchCombineConcatVectors (MachineInstr &MI, SmallVector< Register > &Ops) |

If MI is G_CONCAT_VECTORS, try to combine it. | |

| void | applyCombineConcatVectors (MachineInstr &MI, SmallVector< Register > &Ops) |

Replace MI with a flattened build_vector with Ops or an implicit_def if Ops is empty. | |

| bool | matchCombineShuffleConcat (MachineInstr &MI, SmallVector< Register > &Ops) |

| void | applyCombineShuffleConcat (MachineInstr &MI, SmallVector< Register > &Ops) |

Replace MI with a flattened build_vector with Ops or an implicit_def if Ops is empty. | |

| bool | tryCombineShuffleVector (MachineInstr &MI) |

| Try to combine G_SHUFFLE_VECTOR into G_CONCAT_VECTORS. | |

| bool | matchCombineShuffleVector (MachineInstr &MI, SmallVectorImpl< Register > &Ops) |

Check if the G_SHUFFLE_VECTOR MI can be replaced by a concat_vectors. | |

| void | applyCombineShuffleVector (MachineInstr &MI, const ArrayRef< Register > Ops) |

Replace MI with a concat_vectors with Ops. | |

| bool | matchShuffleToExtract (MachineInstr &MI) |

| void | applyShuffleToExtract (MachineInstr &MI) |

| bool | tryCombineMemCpyFamily (MachineInstr &MI, unsigned MaxLen=0) |

| Optimize memcpy intrinsics et al, e.g. | |

| bool | matchPtrAddImmedChain (MachineInstr &MI, PtrAddChain &MatchInfo) |

| void | applyPtrAddImmedChain (MachineInstr &MI, PtrAddChain &MatchInfo) |

| bool | matchShiftImmedChain (MachineInstr &MI, RegisterImmPair &MatchInfo) |

| Fold (shift (shift base, x), y) -> (shift base (x+y)) | |

| void | applyShiftImmedChain (MachineInstr &MI, RegisterImmPair &MatchInfo) |

| bool | matchShiftOfShiftedLogic (MachineInstr &MI, ShiftOfShiftedLogic &MatchInfo) |

| If we have a shift-by-constant of a bitwise logic op that itself has a shift-by-constant operand with identical opcode, we may be able to convert that into 2 independent shifts followed by the logic op. | |

| void | applyShiftOfShiftedLogic (MachineInstr &MI, ShiftOfShiftedLogic &MatchInfo) |

| bool | matchCommuteShift (MachineInstr &MI, BuildFnTy &MatchInfo) |

| bool | matchCombineMulToShl (MachineInstr &MI, unsigned &ShiftVal) |

| Transform a multiply by a power-of-2 value to a left shift. | |

| void | applyCombineMulToShl (MachineInstr &MI, unsigned &ShiftVal) |

| bool | matchCombineShlOfExtend (MachineInstr &MI, RegisterImmPair &MatchData) |

| void | applyCombineShlOfExtend (MachineInstr &MI, const RegisterImmPair &MatchData) |

| bool | matchCombineMergeUnmerge (MachineInstr &MI, Register &MatchInfo) |

| Fold away a merge of an unmerge of the corresponding values. | |

| bool | matchCombineShiftToUnmerge (MachineInstr &MI, unsigned TargetShiftSize, unsigned &ShiftVal) |

| Reduce a shift by a constant to an unmerge and a shift on a half sized type. | |

| void | applyCombineShiftToUnmerge (MachineInstr &MI, const unsigned &ShiftVal) |

| bool | tryCombineShiftToUnmerge (MachineInstr &MI, unsigned TargetShiftAmount) |

| bool | matchCombineUnmergeMergeToPlainValues (MachineInstr &MI, SmallVectorImpl< Register > &Operands) |

| Transform <ty,...> G_UNMERGE(G_MERGE ty X, Y, Z) -> ty X, Y, Z. | |

| void | applyCombineUnmergeMergeToPlainValues (MachineInstr &MI, SmallVectorImpl< Register > &Operands) |

| bool | matchCombineUnmergeConstant (MachineInstr &MI, SmallVectorImpl< APInt > &Csts) |

| Transform G_UNMERGE Constant -> Constant1, Constant2, ... | |

| void | applyCombineUnmergeConstant (MachineInstr &MI, SmallVectorImpl< APInt > &Csts) |

| bool | matchCombineUnmergeUndef (MachineInstr &MI, std::function< void(MachineIRBuilder &)> &MatchInfo) |

| Transform G_UNMERGE G_IMPLICIT_DEF -> G_IMPLICIT_DEF, G_IMPLICIT_DEF, ... | |

| bool | matchCombineUnmergeWithDeadLanesToTrunc (MachineInstr &MI) |

| Transform X, Y<dead> = G_UNMERGE Z -> X = G_TRUNC Z. | |

| void | applyCombineUnmergeWithDeadLanesToTrunc (MachineInstr &MI) |

| bool | matchCombineUnmergeZExtToZExt (MachineInstr &MI) |

| Transform X, Y = G_UNMERGE(G_ZEXT(Z)) -> X = G_ZEXT(Z); Y = G_CONSTANT 0. | |

| void | applyCombineUnmergeZExtToZExt (MachineInstr &MI) |

| void | applyCombineConstantFoldFpUnary (MachineInstr &MI, const ConstantFP *Cst) |

| Transform fp_instr(cst) to constant result of the fp operation. | |

| bool | matchCombineI2PToP2I (MachineInstr &MI, Register &Reg) |

| Transform IntToPtr(PtrToInt(x)) to x if cast is in the same address space. | |

| void | applyCombineI2PToP2I (MachineInstr &MI, Register &Reg) |

| void | applyCombineP2IToI2P (MachineInstr &MI, Register &Reg) |

| Transform PtrToInt(IntToPtr(x)) to x. | |

| bool | matchCombineAddP2IToPtrAdd (MachineInstr &MI, std::pair< Register, bool > &PtrRegAndCommute) |

| Transform G_ADD (G_PTRTOINT x), y -> G_PTRTOINT (G_PTR_ADD x, y) Transform G_ADD y, (G_PTRTOINT x) -> G_PTRTOINT (G_PTR_ADD x, y) | |

| void | applyCombineAddP2IToPtrAdd (MachineInstr &MI, std::pair< Register, bool > &PtrRegAndCommute) |

| bool | matchCombineConstPtrAddToI2P (MachineInstr &MI, APInt &NewCst) |

| void | applyCombineConstPtrAddToI2P (MachineInstr &MI, APInt &NewCst) |

| bool | matchCombineAnyExtTrunc (MachineInstr &MI, Register &Reg) |

| Transform anyext(trunc(x)) to x. | |

| bool | matchCombineZextTrunc (MachineInstr &MI, Register &Reg) |

| Transform zext(trunc(x)) to x. | |

| bool | matchCombineExtOfExt (MachineInstr &MI, std::tuple< Register, unsigned > &MatchInfo) |

| Transform [asz]ext([asz]ext(x)) to [asz]ext x. | |

| void | applyCombineExtOfExt (MachineInstr &MI, std::tuple< Register, unsigned > &MatchInfo) |

| bool | matchCombineTruncOfShift (MachineInstr &MI, std::pair< MachineInstr *, LLT > &MatchInfo) |

| Transform trunc (shl x, K) to shl (trunc x), K if K < VT.getScalarSizeInBits(). | |

| void | applyCombineTruncOfShift (MachineInstr &MI, std::pair< MachineInstr *, LLT > &MatchInfo) |

| bool | matchAnyExplicitUseIsUndef (MachineInstr &MI) |

Return true if any explicit use operand on MI is defined by a G_IMPLICIT_DEF. | |

| bool | matchAllExplicitUsesAreUndef (MachineInstr &MI) |

Return true if all register explicit use operands on MI are defined by a G_IMPLICIT_DEF. | |

| bool | matchUndefShuffleVectorMask (MachineInstr &MI) |

Return true if a G_SHUFFLE_VECTOR instruction MI has an undef mask. | |

| bool | matchUndefStore (MachineInstr &MI) |

Return true if a G_STORE instruction MI is storing an undef value. | |

| bool | matchUndefSelectCmp (MachineInstr &MI) |

Return true if a G_SELECT instruction MI has an undef comparison. | |

| bool | matchInsertExtractVecEltOutOfBounds (MachineInstr &MI) |

| Return true if a G_{EXTRACT,INSERT}_VECTOR_ELT has an out of range index. | |

| bool | matchConstantSelectCmp (MachineInstr &MI, unsigned &OpIdx) |

Return true if a G_SELECT instruction MI has a constant comparison. | |

| void | replaceInstWithFConstant (MachineInstr &MI, double C) |

Replace an instruction with a G_FCONSTANT with value C. | |

| void | replaceInstWithFConstant (MachineInstr &MI, ConstantFP *CFP) |

Replace an instruction with an G_FCONSTANT with value CFP. | |

| void | replaceInstWithConstant (MachineInstr &MI, int64_t C) |

Replace an instruction with a G_CONSTANT with value C. | |

| void | replaceInstWithConstant (MachineInstr &MI, APInt C) |

Replace an instruction with a G_CONSTANT with value C. | |

| void | replaceInstWithUndef (MachineInstr &MI) |

| Replace an instruction with a G_IMPLICIT_DEF. | |

| void | replaceSingleDefInstWithOperand (MachineInstr &MI, unsigned OpIdx) |

Delete MI and replace all of its uses with its OpIdx-th operand. | |

| void | replaceSingleDefInstWithReg (MachineInstr &MI, Register Replacement) |

Delete MI and replace all of its uses with Replacement. | |

| void | applyFunnelShiftConstantModulo (MachineInstr &MI) |

Replaces the shift amount in MI with ShiftAmt % BW. | |

| bool | matchEqualDefs (const MachineOperand &MOP1, const MachineOperand &MOP2) |

Return true if MOP1 and MOP2 are register operands are defined by equivalent instructions. | |

| bool | matchConstantOp (const MachineOperand &MOP, int64_t C) |

Return true if MOP is defined by a G_CONSTANT or splat with a value equal to C. | |

| bool | matchConstantFPOp (const MachineOperand &MOP, double C) |

Return true if MOP is defined by a G_FCONSTANT or splat with a value exactly equal to C. | |

| bool | matchConstantLargerBitWidth (MachineInstr &MI, unsigned ConstIdx) |

Checks if constant at ConstIdx is larger than MI 's bitwidth. | |

| bool | matchSelectSameVal (MachineInstr &MI) |

| Optimize (cond ? x : x) -> x. | |

| bool | matchBinOpSameVal (MachineInstr &MI) |

| Optimize (x op x) -> x. | |

| bool | matchOperandIsZero (MachineInstr &MI, unsigned OpIdx) |

Check if operand OpIdx is zero. | |

| bool | matchOperandIsUndef (MachineInstr &MI, unsigned OpIdx) |

Check if operand OpIdx is undef. | |

| bool | matchOperandIsKnownToBeAPowerOfTwo (MachineInstr &MI, unsigned OpIdx) |

Check if operand OpIdx is known to be a power of 2. | |

| void | eraseInst (MachineInstr &MI) |

Erase MI. | |

| bool | matchSimplifyAddToSub (MachineInstr &MI, std::tuple< Register, Register > &MatchInfo) |

| Return true if MI is a G_ADD which can be simplified to a G_SUB. | |

| void | applySimplifyAddToSub (MachineInstr &MI, std::tuple< Register, Register > &MatchInfo) |

| bool | matchHoistLogicOpWithSameOpcodeHands (MachineInstr &MI, InstructionStepsMatchInfo &MatchInfo) |

| Match (logic_op (op x...), (op y...)) -> (op (logic_op x, y)) | |

| void | applyBuildInstructionSteps (MachineInstr &MI, InstructionStepsMatchInfo &MatchInfo) |

Replace MI with a series of instructions described in MatchInfo. | |

| bool | matchAshrShlToSextInreg (MachineInstr &MI, std::tuple< Register, int64_t > &MatchInfo) |

| Match ashr (shl x, C), C -> sext_inreg (C) | |

| void | applyAshShlToSextInreg (MachineInstr &MI, std::tuple< Register, int64_t > &MatchInfo) |

| bool | matchOverlappingAnd (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Fold and(and(x, C1), C2) -> C1&C2 ? and(x, C1&C2) : 0. | |

| bool | matchRedundantAnd (MachineInstr &MI, Register &Replacement) |

| bool | matchRedundantOr (MachineInstr &MI, Register &Replacement) |

| bool | matchRedundantSExtInReg (MachineInstr &MI) |

| bool | matchNotCmp (MachineInstr &MI, SmallVectorImpl< Register > &RegsToNegate) |

| Combine inverting a result of a compare into the opposite cond code. | |

| void | applyNotCmp (MachineInstr &MI, SmallVectorImpl< Register > &RegsToNegate) |

| bool | matchXorOfAndWithSameReg (MachineInstr &MI, std::pair< Register, Register > &MatchInfo) |

| Fold (xor (and x, y), y) -> (and (not x), y) {. | |

| void | applyXorOfAndWithSameReg (MachineInstr &MI, std::pair< Register, Register > &MatchInfo) |

| bool | matchPtrAddZero (MachineInstr &MI) |

| } | |

| void | applyPtrAddZero (MachineInstr &MI) |

| void | applySimplifyURemByPow2 (MachineInstr &MI) |

| Combine G_UREM x, (known power of 2) to an add and bitmasking. | |

| bool | matchFoldBinOpIntoSelect (MachineInstr &MI, unsigned &SelectOpNo) |

| Push a binary operator through a select on constants. | |

| void | applyFoldBinOpIntoSelect (MachineInstr &MI, const unsigned &SelectOpNo) |

SelectOperand is the operand in binary operator MI that is the select to fold. | |

| bool | matchCombineInsertVecElts (MachineInstr &MI, SmallVectorImpl< Register > &MatchInfo) |

| void | applyCombineInsertVecElts (MachineInstr &MI, SmallVectorImpl< Register > &MatchInfo) |

| bool | matchLoadOrCombine (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Match expression trees of the form. | |

| bool | matchExtendThroughPhis (MachineInstr &MI, MachineInstr *&ExtMI) |

| void | applyExtendThroughPhis (MachineInstr &MI, MachineInstr *&ExtMI) |

| bool | matchExtractVecEltBuildVec (MachineInstr &MI, Register &Reg) |

| void | applyExtractVecEltBuildVec (MachineInstr &MI, Register &Reg) |

| bool | matchExtractAllEltsFromBuildVector (MachineInstr &MI, SmallVectorImpl< std::pair< Register, MachineInstr * > > &MatchInfo) |

| void | applyExtractAllEltsFromBuildVector (MachineInstr &MI, SmallVectorImpl< std::pair< Register, MachineInstr * > > &MatchInfo) |

| void | applyBuildFn (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Use a function which takes in a MachineIRBuilder to perform a combine. | |

| void | applyBuildFnNoErase (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Use a function which takes in a MachineIRBuilder to perform a combine. | |

| bool | matchOrShiftToFunnelShift (MachineInstr &MI, BuildFnTy &MatchInfo) |

| bool | matchFunnelShiftToRotate (MachineInstr &MI) |

| Match an FSHL or FSHR that can be combined to a ROTR or ROTL rotate. | |

| void | applyFunnelShiftToRotate (MachineInstr &MI) |

| bool | matchRotateOutOfRange (MachineInstr &MI) |

| void | applyRotateOutOfRange (MachineInstr &MI) |

| bool | matchICmpToTrueFalseKnownBits (MachineInstr &MI, int64_t &MatchInfo) |

| bool | matchICmpToLHSKnownBits (MachineInstr &MI, BuildFnTy &MatchInfo) |

| bool | matchAndOrDisjointMask (MachineInstr &MI, BuildFnTy &MatchInfo) |

| bool | matchBitfieldExtractFromSExtInReg (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Form a G_SBFX from a G_SEXT_INREG fed by a right shift. | |

| bool | matchBitfieldExtractFromAnd (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Match: and (lshr x, cst), mask -> ubfx x, cst, width. | |

| bool | matchBitfieldExtractFromShr (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Match: shr (shl x, n), k -> sbfx/ubfx x, pos, width. | |

| bool | matchBitfieldExtractFromShrAnd (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Match: shr (and x, n), k -> ubfx x, pos, width. | |

| bool | matchReassocConstantInnerRHS (GPtrAdd &MI, MachineInstr *RHS, BuildFnTy &MatchInfo) |

| bool | matchReassocFoldConstantsInSubTree (GPtrAdd &MI, MachineInstr *LHS, MachineInstr *RHS, BuildFnTy &MatchInfo) |

| bool | matchReassocConstantInnerLHS (GPtrAdd &MI, MachineInstr *LHS, MachineInstr *RHS, BuildFnTy &MatchInfo) |

| bool | matchReassocPtrAdd (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Reassociate pointer calculations with G_ADD involved, to allow better addressing mode usage. | |

| bool | tryReassocBinOp (unsigned Opc, Register DstReg, Register Op0, Register Op1, BuildFnTy &MatchInfo) |

| Try to reassociate to reassociate operands of a commutative binop. | |

| bool | matchReassocCommBinOp (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Reassociate commutative binary operations like G_ADD. | |

| bool | matchConstantFoldCastOp (MachineInstr &MI, APInt &MatchInfo) |

| Do constant folding when opportunities are exposed after MIR building. | |

| bool | matchConstantFoldBinOp (MachineInstr &MI, APInt &MatchInfo) |

| Do constant folding when opportunities are exposed after MIR building. | |

| bool | matchConstantFoldFPBinOp (MachineInstr &MI, ConstantFP *&MatchInfo) |

| Do constant FP folding when opportunities are exposed after MIR building. | |

| bool | matchConstantFoldFMA (MachineInstr &MI, ConstantFP *&MatchInfo) |

| Constant fold G_FMA/G_FMAD. | |

| bool | matchNarrowBinopFeedingAnd (MachineInstr &MI, BuildFnTy &MatchInfo) |

| MachineInstr * | buildUDivUsingMul (MachineInstr &MI) |

Given an G_UDIV MI expressing a divide by constant, return an expression that implements it by multiplying by a magic number. | |

| bool | matchUDivByConst (MachineInstr &MI) |

| Combine G_UDIV by constant into a multiply by magic constant. | |

| void | applyUDivByConst (MachineInstr &MI) |

| MachineInstr * | buildSDivUsingMul (MachineInstr &MI) |

Given an G_SDIV MI expressing a signed divide by constant, return an expression that implements it by multiplying by a magic number. | |

| bool | matchSDivByConst (MachineInstr &MI) |

| void | applySDivByConst (MachineInstr &MI) |

| bool | matchDivByPow2 (MachineInstr &MI, bool IsSigned) |

Given an G_SDIV MI expressing a signed divided by a pow2 constant, return expressions that implements it by shifting. | |

| void | applySDivByPow2 (MachineInstr &MI) |

| void | applyUDivByPow2 (MachineInstr &MI) |

Given an G_UDIV MI expressing an unsigned divided by a pow2 constant, return expressions that implements it by shifting. | |

| bool | matchUMulHToLShr (MachineInstr &MI) |

| void | applyUMulHToLShr (MachineInstr &MI) |

| bool | tryCombine (MachineInstr &MI) |

Try to transform MI by using all of the above combine functions. | |

| bool | tryEmitMemcpyInline (MachineInstr &MI) |

| Emit loads and stores that perform the given memcpy. | |

| bool | matchMulOBy2 (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Match: (G_UMULO x, 2) -> (G_UADDO x, x) (G_SMULO x, 2) -> (G_SADDO x, x) | |

| bool | matchMulOBy0 (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Match: (G_*MULO x, 0) -> 0 + no carry out. | |

| bool | matchAddEToAddO (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Match: (G_*ADDE x, y, 0) -> (G_*ADDO x, y) (G_*SUBE x, y, 0) -> (G_*SUBO x, y) | |

| bool | matchRedundantNegOperands (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Transform (fadd x, fneg(y)) -> (fsub x, y) (fadd fneg(x), y) -> (fsub y, x) (fsub x, fneg(y)) -> (fadd x, y) (fmul fneg(x), fneg(y)) -> (fmul x, y) (fdiv fneg(x), fneg(y)) -> (fdiv x, y) (fmad fneg(x), fneg(y), z) -> (fmad x, y, z) (fma fneg(x), fneg(y), z) -> (fma x, y, z) | |

| bool | matchFsubToFneg (MachineInstr &MI, Register &MatchInfo) |

| void | applyFsubToFneg (MachineInstr &MI, Register &MatchInfo) |

| bool | canCombineFMadOrFMA (MachineInstr &MI, bool &AllowFusionGlobally, bool &HasFMAD, bool &Aggressive, bool CanReassociate=false) |

| bool | matchCombineFAddFMulToFMadOrFMA (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Transform (fadd (fmul x, y), z) -> (fma x, y, z) (fadd (fmul x, y), z) -> (fmad x, y, z) | |

| bool | matchCombineFAddFpExtFMulToFMadOrFMA (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Transform (fadd (fpext (fmul x, y)), z) -> (fma (fpext x), (fpext y), z) (fadd (fpext (fmul x, y)), z) -> (fmad (fpext x), (fpext y), z) | |

| bool | matchCombineFAddFMAFMulToFMadOrFMA (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Transform (fadd (fma x, y, (fmul u, v)), z) -> (fma x, y, (fma u, v, z)) (fadd (fmad x, y, (fmul u, v)), z) -> (fmad x, y, (fmad u, v, z)) | |

| bool | matchCombineFAddFpExtFMulToFMadOrFMAAggressive (MachineInstr &MI, BuildFnTy &MatchInfo) |

| bool | matchCombineFSubFMulToFMadOrFMA (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Transform (fsub (fmul x, y), z) -> (fma x, y, -z) (fsub (fmul x, y), z) -> (fmad x, y, -z) | |

| bool | matchCombineFSubFNegFMulToFMadOrFMA (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Transform (fsub (fneg (fmul, x, y)), z) -> (fma (fneg x), y, (fneg z)) (fsub (fneg (fmul, x, y)), z) -> (fmad (fneg x), y, (fneg z)) | |

| bool | matchCombineFSubFpExtFMulToFMadOrFMA (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Transform (fsub (fpext (fmul x, y)), z) -> (fma (fpext x), (fpext y), (fneg z)) (fsub (fpext (fmul x, y)), z) -> (fmad (fpext x), (fpext y), (fneg z)) | |

| bool | matchCombineFSubFpExtFNegFMulToFMadOrFMA (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Transform (fsub (fpext (fneg (fmul x, y))), z) -> (fneg (fma (fpext x), (fpext y), z)) (fsub (fpext (fneg (fmul x, y))), z) -> (fneg (fmad (fpext x), (fpext y), z)) | |

| bool | matchCombineFMinMaxNaN (MachineInstr &MI, unsigned &Info) |

| bool | matchAddSubSameReg (MachineInstr &MI, Register &Src) |

| Transform G_ADD(x, G_SUB(y, x)) to y. | |

| bool | matchBuildVectorIdentityFold (MachineInstr &MI, Register &MatchInfo) |

| bool | matchTruncBuildVectorFold (MachineInstr &MI, Register &MatchInfo) |

| bool | matchTruncLshrBuildVectorFold (MachineInstr &MI, Register &MatchInfo) |

| bool | matchSubAddSameReg (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Transform: (x + y) - y -> x (x + y) - x -> y x - (y + x) -> 0 - y x - (x + z) -> 0 - z. | |

| bool | matchSimplifySelectToMinMax (MachineInstr &MI, BuildFnTy &MatchInfo) |

| bool | matchRedundantBinOpInEquality (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Transform: (X + Y) == X -> Y == 0 (X - Y) == X -> Y == 0 (X ^ Y) == X -> Y == 0 (X + Y) != X -> Y != 0 (X - Y) != X -> Y != 0 (X ^ Y) != X -> Y != 0. | |

| bool | matchShiftsTooBig (MachineInstr &MI) |

| Match shifts greater or equal to the bitwidth of the operation. | |

| bool | matchCommuteConstantToRHS (MachineInstr &MI) |

| Match constant LHS ops that should be commuted. | |

| bool | matchSextOfTrunc (const MachineOperand &MO, BuildFnTy &MatchInfo) |

| Combine sext of trunc. | |

| bool | matchZextOfTrunc (const MachineOperand &MO, BuildFnTy &MatchInfo) |

| Combine zext of trunc. | |

| bool | matchNonNegZext (const MachineOperand &MO, BuildFnTy &MatchInfo) |

| Combine zext nneg to sext. | |

| bool | matchCommuteFPConstantToRHS (MachineInstr &MI) |

| Match constant LHS FP ops that should be commuted. | |

| void | applyCommuteBinOpOperands (MachineInstr &MI) |

| bool | matchSelectIMinMax (const MachineOperand &MO, BuildFnTy &MatchInfo) |

| Combine select to integer min/max. | |

| bool | matchSelect (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Combine selects. | |

| bool | matchAnd (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Combine ands. | |

| bool | matchOr (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Combine ors. | |

| bool | matchAddOverflow (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Combine addos. | |

| bool | matchExtractVectorElement (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Combine extract vector element. | |

| bool | matchExtractVectorElementWithBuildVector (const MachineOperand &MO, BuildFnTy &MatchInfo) |

| Combine extract vector element with a build vector on the vector register. | |

| bool | matchExtractVectorElementWithBuildVectorTrunc (const MachineOperand &MO, BuildFnTy &MatchInfo) |

| Combine extract vector element with a build vector trunc on the vector register. | |

| bool | matchExtractVectorElementWithShuffleVector (const MachineOperand &MO, BuildFnTy &MatchInfo) |

| Combine extract vector element with a shuffle vector on the vector register. | |

| bool | matchExtractVectorElementWithDifferentIndices (const MachineOperand &MO, BuildFnTy &MatchInfo) |

| Combine extract vector element with a insert vector element on the vector register and different indices. | |

| void | applyBuildFnMO (const MachineOperand &MO, BuildFnTy &MatchInfo) |

| Use a function which takes in a MachineIRBuilder to perform a combine. | |

| bool | matchFPowIExpansion (MachineInstr &MI, int64_t Exponent) |

| Match FPOWI if it's safe to extend it into a series of multiplications. | |

| void | applyExpandFPowI (MachineInstr &MI, int64_t Exponent) |

| Expands FPOWI into a series of multiplications and a division if the exponent is negative. | |

| bool | matchInsertVectorElementOOB (MachineInstr &MI, BuildFnTy &MatchInfo) |

| Combine insert vector element OOB. | |

| bool | matchFreezeOfSingleMaybePoisonOperand (MachineInstr &MI, BuildFnTy &MatchInfo) |

| bool | matchAddOfVScale (const MachineOperand &MO, BuildFnTy &MatchInfo) |

| bool | matchMulOfVScale (const MachineOperand &MO, BuildFnTy &MatchInfo) |

| bool | matchSubOfVScale (const MachineOperand &MO, BuildFnTy &MatchInfo) |

| bool | matchShlOfVScale (const MachineOperand &MO, BuildFnTy &MatchInfo) |

| bool | matchTruncateOfExt (const MachineInstr &Root, const MachineInstr &ExtMI, BuildFnTy &MatchInfo) |

| Transform trunc ([asz]ext x) to x or ([asz]ext x) or (trunc x). | |

Additional Inherited Members | |

Protected Attributes inherited from llvm::CombinerHelper Protected Attributes inherited from llvm::CombinerHelper | |

| MachineIRBuilder & | Builder |

| MachineRegisterInfo & | MRI |

| GISelChangeObserver & | Observer |

| GISelKnownBits * | KB |

| MachineDominatorTree * | MDT |

| bool | IsPreLegalize |

| const LegalizerInfo * | LI |

| const RegisterBankInfo * | RBI |

| const TargetRegisterInfo * | TRI |

Detailed Description

Definition at line 23 of file AMDGPUCombinerHelper.h.

Member Function Documentation

◆ applyExpandPromotedF16FMed3()

| void AMDGPUCombinerHelper::applyExpandPromotedF16FMed3 | ( | MachineInstr & | MI, |

| Register | Src0, | ||

| Register | Src1, | ||

| Register | Src2 | ||

| ) |

Definition at line 431 of file AMDGPUCombinerHelper.cpp.

References llvm::CombinerHelper::Builder, llvm::MachineIRBuilder::buildFMaxNumIEEE(), llvm::MachineIRBuilder::buildFMinNumIEEE(), llvm::MachineIRBuilder::buildFPTrunc(), llvm::MachineInstrBuilder::getReg(), llvm::MachineRegisterInfo::getType(), MI, llvm::CombinerHelper::MRI, and llvm::LLT::scalar().

◆ applyFoldableFneg()

| void AMDGPUCombinerHelper::applyFoldableFneg | ( | MachineInstr & | MI, |

| MachineInstr *& | MatchInfo | ||

| ) |

Definition at line 261 of file AMDGPUCombinerHelper.cpp.

References llvm::CombinerHelper::Builder, llvm::MachineIRBuilder::buildFNeg(), llvm::MachineRegisterInfo::createGenericVirtualRegister(), llvm::ilist_node_impl< OptionsT >::getIterator(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), getReg(), llvm::MachineRegisterInfo::getType(), llvm::MachineRegisterInfo::hasOneNonDBGUse(), inverseMinMax(), llvm_unreachable, llvm::MIPatternMatch::m_GFNeg(), llvm::MIPatternMatch::m_Reg(), MI, llvm::MIPatternMatch::mi_match(), llvm::CombinerHelper::MRI, llvm::CombinerHelper::replaceOpcodeWith(), llvm::CombinerHelper::replaceRegOpWith(), llvm::CombinerHelper::replaceRegWith(), llvm::MachineIRBuilder::setInstrAndDebugLoc(), X, and Y.

◆ matchExpandPromotedF16FMed3()

| bool AMDGPUCombinerHelper::matchExpandPromotedF16FMed3 | ( | MachineInstr & | MI, |

| Register | Src0, | ||

| Register | Src1, | ||

| Register | Src2 | ||

| ) |

Definition at line 418 of file AMDGPUCombinerHelper.cpp.

References assert(), llvm::MachineRegisterInfo::getType(), llvm::MachineRegisterInfo::hasOneNonDBGUse(), isFPExtFromF16OrConst(), MI, llvm::CombinerHelper::MRI, and llvm::LLT::scalar().

◆ matchFoldableFneg()

| bool AMDGPUCombinerHelper::matchFoldableFneg | ( | MachineInstr & | MI, |

| MachineInstr *& | MatchInfo | ||

| ) |

Definition at line 192 of file AMDGPUCombinerHelper.cpp.

References allUsesHaveSourceMods(), fnegFoldsIntoMI(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getVRegDef(), llvm::MachineRegisterInfo::hasOneNonDBGUse(), isConstantCostlierToNegate(), mayIgnoreSignedZero(), MI, and llvm::CombinerHelper::MRI.

The documentation for this class was generated from the following files:

- lib/Target/AMDGPU/AMDGPUCombinerHelper.h

- lib/Target/AMDGPU/AMDGPUCombinerHelper.cpp