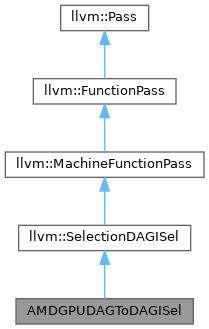

AMDGPU specific code to select AMDGPU machine instructions for SelectionDAG operations. More...

#include "Target/AMDGPU/AMDGPUISelDAGToDAG.h"

Public Member Functions | |

| AMDGPUDAGToDAGISel ()=delete | |

| AMDGPUDAGToDAGISel (TargetMachine &TM, CodeGenOptLevel OptLevel) | |

| bool | runOnMachineFunction (MachineFunction &MF) override |

| bool | matchLoadD16FromBuildVector (SDNode *N) const |

| void | PreprocessISelDAG () override |

| PreprocessISelDAG - This hook allows targets to hack on the graph before instruction selection starts. | |

| void | Select (SDNode *N) override |

| Main hook for targets to transform nodes into machine nodes. | |

| void | PostprocessISelDAG () override |

| PostprocessISelDAG() - This hook allows the target to hack on the graph right after selection. | |

Public Member Functions inherited from llvm::SelectionDAGISel Public Member Functions inherited from llvm::SelectionDAGISel | |

| SelectionDAGISel (TargetMachine &tm, CodeGenOptLevel OL=CodeGenOptLevel::Default) | |

| virtual | ~SelectionDAGISel () |

| const TargetLowering * | getTargetLowering () const |

| void | initializeAnalysisResults (MachineFunctionAnalysisManager &MFAM) |

| void | initializeAnalysisResults (MachineFunctionPass &MFP) |

| virtual bool | runOnMachineFunction (MachineFunction &mf) |

| virtual void | emitFunctionEntryCode () |

| virtual void | PreprocessISelDAG () |

| PreprocessISelDAG - This hook allows targets to hack on the graph before instruction selection starts. | |

| virtual void | PostprocessISelDAG () |

| PostprocessISelDAG() - This hook allows the target to hack on the graph right after selection. | |

| virtual void | Select (SDNode *N)=0 |

| Main hook for targets to transform nodes into machine nodes. | |

| virtual bool | SelectInlineAsmMemoryOperand (const SDValue &Op, InlineAsm::ConstraintCode ConstraintID, std::vector< SDValue > &OutOps) |

| SelectInlineAsmMemoryOperand - Select the specified address as a target addressing mode, according to the specified constraint. | |

| virtual bool | IsProfitableToFold (SDValue N, SDNode *U, SDNode *Root) const |

| IsProfitableToFold - Returns true if it's profitable to fold the specific operand node N of U during instruction selection that starts at Root. | |

| bool | CheckAndMask (SDValue LHS, ConstantSDNode *RHS, int64_t DesiredMaskS) const |

| CheckAndMask - The isel is trying to match something like (and X, 255). | |

| bool | CheckOrMask (SDValue LHS, ConstantSDNode *RHS, int64_t DesiredMaskS) const |

| CheckOrMask - The isel is trying to match something like (or X, 255). | |

| virtual bool | CheckPatternPredicate (unsigned PredNo) const |

| CheckPatternPredicate - This function is generated by tblgen in the target. | |

| virtual bool | CheckNodePredicate (SDNode *N, unsigned PredNo) const |

| CheckNodePredicate - This function is generated by tblgen in the target. | |

| virtual bool | CheckNodePredicateWithOperands (SDNode *N, unsigned PredNo, const SmallVectorImpl< SDValue > &Operands) const |

| CheckNodePredicateWithOperands - This function is generated by tblgen in the target. | |

| virtual bool | CheckComplexPattern (SDNode *Root, SDNode *Parent, SDValue N, unsigned PatternNo, SmallVectorImpl< std::pair< SDValue, SDNode * > > &Result) |

| virtual SDValue | RunSDNodeXForm (SDValue V, unsigned XFormNo) |

| void | SelectCodeCommon (SDNode *NodeToMatch, const unsigned char *MatcherTable, unsigned TableSize) |

| virtual bool | ComplexPatternFuncMutatesDAG () const |

| Return true if complex patterns for this target can mutate the DAG. | |

| bool | mayRaiseFPException (SDNode *Node) const |

| Return whether the node may raise an FP exception. | |

| bool | isOrEquivalentToAdd (const SDNode *N) const |

Protected Member Functions | |

| void | SelectBuildVector (SDNode *N, unsigned RegClassID) |

Protected Member Functions inherited from llvm::SelectionDAGISel Protected Member Functions inherited from llvm::SelectionDAGISel | |

| void | ReplaceUses (SDValue F, SDValue T) |

| ReplaceUses - replace all uses of the old node F with the use of the new node T. | |

| void | ReplaceUses (const SDValue *F, const SDValue *T, unsigned Num) |

| ReplaceUses - replace all uses of the old nodes F with the use of the new nodes T. | |

| void | ReplaceUses (SDNode *F, SDNode *T) |

| ReplaceUses - replace all uses of the old node F with the use of the new node T. | |

| void | ReplaceNode (SDNode *F, SDNode *T) |

Replace all uses of F with T, then remove F from the DAG. | |

| void | SelectInlineAsmMemoryOperands (std::vector< SDValue > &Ops, const SDLoc &DL) |

| SelectInlineAsmMemoryOperands - Calls to this are automatically generated by tblgen. | |

| virtual StringRef | getPatternForIndex (unsigned index) |

| getPatternForIndex - Patterns selected by tablegen during ISEL | |

| virtual StringRef | getIncludePathForIndex (unsigned index) |

| getIncludePathForIndex - get the td source location of pattern instantiation | |

| bool | shouldOptForSize (const MachineFunction *MF) const |

Detailed Description

AMDGPU specific code to select AMDGPU machine instructions for SelectionDAG operations.

Definition at line 67 of file AMDGPUISelDAGToDAG.h.

Constructor & Destructor Documentation

◆ AMDGPUDAGToDAGISel() [1/2]

|

delete |

◆ AMDGPUDAGToDAGISel() [2/2]

|

explicit |

Definition at line 122 of file AMDGPUISelDAGToDAG.cpp.

References llvm::AMDGPUTargetMachine::EnableLateStructurizeCFG.

Member Function Documentation

◆ matchLoadD16FromBuildVector()

Definition at line 219 of file AMDGPUISelDAGToDAG.cpp.

References assert(), llvm::ISD::BITCAST, llvm::SelectionDAGISel::CurDAG, llvm::GCNSubtarget::d16PreservesUnusedBits(), llvm::LoadSDNode::getBasePtr(), llvm::MemSDNode::getChain(), llvm::LoadSDNode::getExtensionType(), llvm::SelectionDAG::getMemIntrinsicNode(), llvm::MemSDNode::getMemOperand(), llvm::MemSDNode::getMemoryVT(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::SDValue::getValue(), llvm::SelectionDAG::getVTList(), Hi, llvm::SDNode::isPredecessorOf(), Lo, llvm::AMDGPUISD::LOAD_D16_HI, llvm::AMDGPUISD::LOAD_D16_HI_I8, llvm::AMDGPUISD::LOAD_D16_HI_U8, llvm::AMDGPUISD::LOAD_D16_LO, llvm::AMDGPUISD::LOAD_D16_LO_I8, llvm::AMDGPUISD::LOAD_D16_LO_U8, N, llvm::SelectionDAG::ReplaceAllUsesOfValueWith(), llvm::ISD::SCALAR_TO_VECTOR, and llvm::ISD::SEXTLOAD.

Referenced by PreprocessISelDAG().

◆ PostprocessISelDAG()

|

overridevirtual |

PostprocessISelDAG() - This hook allows the target to hack on the graph right after selection.

Reimplemented from llvm::SelectionDAGISel.

Definition at line 3618 of file AMDGPUISelDAGToDAG.cpp.

References llvm::SelectionDAG::allnodes_begin(), llvm::SelectionDAG::allnodes_end(), llvm::SelectionDAGISel::CurDAG, llvm::SelectionDAGISel::getTargetLowering(), Lowering, llvm::SelectionDAG::RemoveDeadNodes(), and llvm::SelectionDAGISel::ReplaceUses().

◆ PreprocessISelDAG()

|

overridevirtual |

PreprocessISelDAG - This hook allows targets to hack on the graph before instruction selection starts.

Reimplemented from llvm::SelectionDAGISel.

Definition at line 299 of file AMDGPUISelDAGToDAG.cpp.

References llvm::SelectionDAG::allnodes_begin(), llvm::SelectionDAG::allnodes_end(), llvm::ISD::BUILD_VECTOR, llvm::SelectionDAGISel::CurDAG, llvm::GCNSubtarget::d16PreservesUnusedBits(), llvm::dbgs(), llvm::SelectionDAG::dump(), LLVM_DEBUG, matchLoadD16FromBuildVector(), N, and llvm::SelectionDAG::RemoveDeadNodes().

◆ runOnMachineFunction()

|

overridevirtual |

Reimplemented from llvm::SelectionDAGISel.

Definition at line 128 of file AMDGPUISelDAGToDAG.cpp.

References llvm::GCNSubtarget::checkSubtargetFeatures(), llvm::MachineFunction::getFunction(), llvm::MachineFunction::getSubtarget(), llvm::SelectionDAGISel::MF, and llvm::SelectionDAGISel::runOnMachineFunction().

◆ Select()

|

overridevirtual |

Main hook for targets to transform nodes into machine nodes.

Implements llvm::SelectionDAGISel.

Definition at line 496 of file AMDGPUISelDAGToDAG.cpp.

References llvm::ISD::ADDC, llvm::ISD::ADDE, llvm::ISD::AND, assert(), llvm::AMDGPUISD::BFE_I32, llvm::AMDGPUISD::BFE_U32, llvm::EVT::bitsEq(), llvm::ISD::BRCOND, llvm::ISD::BUILD_PAIR, llvm::ISD::BUILD_VECTOR, llvm::CallingConv::C, llvm::ISD::Constant, llvm::ISD::ConstantFP, llvm::ISD::CopyToReg, llvm::SelectionDAGISel::CurDAG, llvm::AMDGPUISD::CVT_PK_I16_I32, llvm::AMDGPUISD::CVT_PK_U16_U32, llvm::AMDGPUISD::CVT_PKNORM_I16_F32, llvm::AMDGPUISD::CVT_PKNORM_U16_F32, llvm::AMDGPUISD::CVT_PKRTZ_F16_F32, llvm::AMDGPUISD::DIV_SCALE, DL, llvm::AMDGPUISD::FMA_W_CHAIN, llvm::AMDGPUISD::FMUL_W_CHAIN, FP, llvm::ISD::FP_EXTEND, llvm::TargetRegisterClass::getID(), llvm::SelectionDAG::getMachineNode(), llvm::EVT::getScalarSizeInBits(), llvm::SIRegisterInfo::getSGPRClassForBitWidth(), llvm::SelectionDAG::getTargetConstant(), llvm::SelectionDAGISel::getTargetLowering(), llvm::EVT::getVectorElementType(), llvm::EVT::getVectorNumElements(), llvm::SelectionDAG::getVTList(), llvm::ConstantSDNode::getZExtValue(), llvm::ISD::INTRINSIC_VOID, llvm::ISD::INTRINSIC_W_CHAIN, llvm::ISD::INTRINSIC_WO_CHAIN, llvm::AMDGPU::isValid32BitLiteral(), llvm_unreachable, llvm::ISD::LOAD, Lowering, llvm::AMDGPUISD::MAD_I64_I32, llvm::AMDGPUISD::MAD_U64_U32, llvm::SelectionDAG::MorphNodeTo(), N, llvm::Offset, llvm::SelectionDAGISel::ReplaceNode(), llvm::ISD::SCALAR_TO_VECTOR, SelectBuildVector(), llvm::ISD::SIGN_EXTEND_INREG, Signed, llvm::ISD::SMUL_LOHI, llvm::ISD::SRA, llvm::ISD::SRL, llvm::ISD::STACKRESTORE, llvm::ISD::STORE, llvm::ISD::SUBC, llvm::ISD::SUBE, llvm::ISD::UADDO, llvm::ISD::UADDO_CARRY, llvm::ISD::UMUL_LOHI, llvm::ISD::USUBO, llvm::ISD::USUBO_CARRY, and llvm::AMDGPUISD::WAVE_ADDRESS.

◆ SelectBuildVector()

Definition at line 441 of file AMDGPUISelDAGToDAG.cpp.

References llvm::Triple::amdgcn, assert(), llvm::SelectionDAGISel::CurDAG, DL, llvm::Triple::getArch(), llvm::SelectionDAG::getMachineNode(), llvm::R600RegisterInfo::getSubRegFromChannel(), llvm::SIRegisterInfo::getSubRegFromChannel(), llvm::SelectionDAG::getSubtarget(), llvm::SelectionDAG::getTargetConstant(), llvm::MCSubtargetInfo::getTargetTriple(), llvm::EVT::getVectorElementType(), llvm::EVT::getVectorNumElements(), N, llvm::ISD::SCALAR_TO_VECTOR, and llvm::SelectionDAG::SelectNodeTo().

Referenced by Select().

The documentation for this class was generated from the following files:

- lib/Target/AMDGPU/AMDGPUISelDAGToDAG.h

- lib/Target/AMDGPU/AMDGPUISelDAGToDAG.cpp